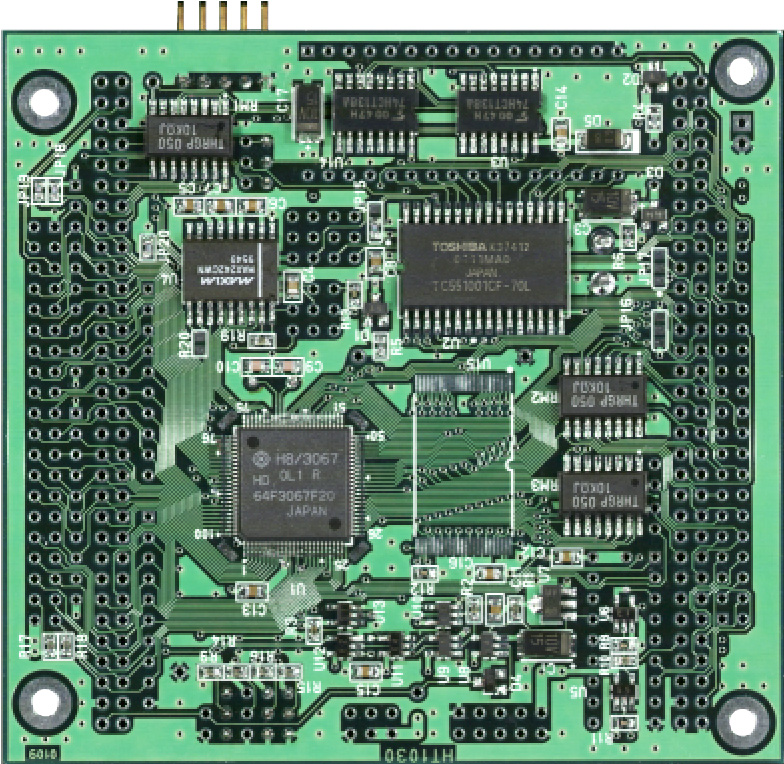

HT1030

H8/3067 CPU

SRAM128KBを標準搭載

CPU内蔵のSRAM4KBでは何かと容量不足になりがちですが、HT1030ではSRAM128KBを標準搭載。また、オプションメモリソケットでさらに512KBのSRAM(DIP)が増設できます※1。

PC/104準拠の拡張バス信号配列

バスコネクタの信号配列はPC/104規格に準じていますので、HTシリーズのオプトアイソレート入出力やRS232C/485等のモジュールをそのままスタック接続して使用できます※1。

またI/O信号はフラットケーブルでの取り出しを考慮し、ボックスピンヘッダ搭載スペースを用意しています。

開発ツールへ簡単接続

ボード上には、ROMインサーキットデバッガ接続用DIPソケット搭載スペース※2を用意しています。また、ICE接続用ソケット搭載モデルもございますので、すでにお使いの開発ツールが活用できます。

ブートモードへの切替はワンタッチ

ボード上の小型スイッチ操作だけでブートモードに切替でき、プログラム書換のたびに動作モードのジャンパ設定を変えたり、スタックしたI/Oモジュールを外す必要がありません。

※1 モジュールによっては、システムクロックを8MHzで動作させる必要があります。

※2 メモリ増設およびROMインサーキットデバッガ接続は同じソケットを使用しますので、同時には対応できません。

HT1030ツールアップデートのお知らせ

HT1030に付属のツール「FLASHWR」を最新バージョンにアップデートします。

以下のページをご覧ください。

HT1030基板改変のお知らせ

以下の内容は2003年12月に告知した内容です。

現在公開のマニュアルには、下記内容も含まれております。

詳しい内容は、下記ドキュメントをご覧ください。

変更内容

HT1030-HENKO.PDF

新回路図

HT1030PUB4.PDF

製品ラインアップ

| HT1030-U00 | H8/3067 CPU RoHS準拠 |

|---|---|

| HT1030-03 | PC接続ケーブル RoHS準拠 |

| HT1030-SKA | 山一電機製ICEソケット搭載開発用モデル RoHS準拠 |

| HT1030-SKB | 東京エレテック製ICEソケット搭載開発用モデル |

仕様

| プロセッサ | ルネサス HD64F3067RF(H8/3067) |

|---|---|

| システムクロック | 16MHz(原発振、分周可能) |

| メモリ | SRAM:4KB(CPU内蔵、バックアップ無)+128KB(バックアップ付) |

| FLASH:128KB(CPU内蔵、書き換え回数100回min) | |

| カレンダ時計 | EPSON RTC62421/63421搭載可能(バックアップ付) |

| シリアルポート | チャンネル0,1:RS232C (チャンネル1はFLASHメモリ書き換えに使用) |

| チャンネル2:TTL レベル | |

| ボーレートジェネレータ | 各チャンネル独立、CPU内蔵 |

| 汎用入出力 | 34ビット(一部ピンは他のI/O機能と重複) |

| A/Dコンバータ | CPU内蔵10ビット8CH(変換時間3.5uS) |

| タイマ | 16ビットタイマ:3CH |

| 8ビットタイマ:4CH | |

| ウォッチドッグタイマ | CPU内蔵 |

| バックアップ | 0.1F電気二重層コンデンサ(電池併用可能) |

| スタンバイ機能 | システムクロック停止可能 ウェイクアップ機能 |

| オプションソケット | DIP32ピン1M,4MbitSRAM/EPROMをボード上に追加実装可能 (ROMインサーキットデバッガ対応) |

| 基板外形サイズ | 90.2×95.9mm(突起部含まず) |

| 電源 | DC5V±5% |

| 消費電流 | 70mA(Typ.)/200mA(Max)/スタンバイ時0.5mA(Typ.)※ |

| 動作温度範囲 | 0~+70℃ |

※外部接続なし、MAX242をシャットダウンした場合