# HT series

# HT3080

ユーザーズマニュアル

## 目次

| 1 はじ    | かに                       | 1    |

|---------|--------------------------|------|

| 2 注意    | 事項                       | 2    |

| 2.1 安全  | 全に関する注意事項                | 2    |

|         | 2扱い上の注意事項                |      |

|         |                          |      |

| 3 XR16  | iL788 概要                 | 3    |

| 4 資料    | ・参考文献                    | 4    |

| 5 テス    | トプログラム                   | 5    |

| 5.1 HT  | 1070/Armadillo-9 との組み合わせ | 5    |

| 5.1.1   | 準備                       | 5    |

| 5.1.2   | RS232C 送受信テスト            | 6    |

| 5.1.3   | RS485 送受信テスト             | 7    |

| 5.2 HT  | 1030/HT1040 との組み合わせ      | 9    |

| 5.2.1   | 準備                       | 9    |

| 5.2.2   | RS232C 送受信テスト            | 9    |

| 5.2.3   | RS232C フロー制御受信テスト        | 10   |

| 5.2.4   | RS485 送受信テスト             | 11   |

| 6 仕様.   |                          | . 13 |

|         |                          |      |

| 7 八一    | ドウェア機能                   | . 14 |

| 7.1 ブロ  | コック図                     | 14   |

| 7.2 🗆 = | ネクタ信号配置・機能               | 15   |

| 7.2.1   | HT3080 コネクタピン配列          | 15   |

| 7.2.2   | バス信号(CN1)                | 16   |

| 7.2.3   | 入出力信号(CN2/CN3)           | . 17 |

| 7.2.4   | コネクタ型式                   | 17   |

| 7.2.5   | オプションケーブル HT3080-01      | . 17 |

| 7.3 ジャ  | ァンパ設定                    | 19   |

| 7.3.1   | JP1 ~ JP4                | 19   |

| 7.3.2   | JP5                      | 20   |

| 7.3.3   | JP6 ~ 9                  | . 20 |

| 7.3.4   | JPn0                     | 21   |

| 7.3.5   | JPn1/JPn2                |      |

| 7.3.6   | JPn3/JPn4                |      |

| 7.3.7   | JPn5                     |      |

| 7.3.8   | JPn6                     |      |

|         | 485 出力ドライバ制御             |      |

|         | 485 ハーフ・フルデュプレクス切替       |      |

|         | イマ外部クロック入力               |      |

| 8 内蔵I   | ノジスタ                     | . 24 |

| 8.1 レ   | ジスタマップ                   | . 24 |

| 8.2  | UART チャンネルコンフィグレーションレジスタ              | 25  |

|------|---------------------------------------|-----|

| 8.2. | 1 RHR                                 | 25  |

| 8.2. | 2 THR                                 | 26  |

| 8.2. | 3 DLL, DLM                            | 26  |

| 8.2. | 4 IER                                 | 26  |

| 8.2. | 5 ISR                                 | 27  |

| 8.2. | 6 FCR                                 | 28  |

| 8.2. | 7 LCR                                 | 29  |

| 8.2. | 8 MCR                                 | 30  |

| 8.2. | 9 LSR                                 | 31  |

| 8.2. | 10 MSR                                | 31  |

| 8.2. | 11 RS485DLY                           | 32  |

| 8.2. | 12 SPR                                | 32  |

| 8.2. | 13 FCTR                               | 32  |

| 8.2. | 14 EFR                                | 33  |

| 8.2. | 15 TXCNT                              | 35  |

| 8.2. | 16 TXTRG                              | 35  |

| 8.2. | 17 RXCNT                              | 35  |

| 8.2. | 18 RXTRG                              | 35  |

| 8.2. | 19 XCHAR                              | 35  |

| 8.2. |                                       |     |

| 8.2. |                                       |     |

| 8.2. |                                       | -   |

| 8.2. |                                       |     |

| 8.3  | デバイスコンフィグレーションレジスタ                    |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. | · · · · · · · · · · · · · · · · · · · |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

| 8.3. |                                       |     |

|      |                                       |     |

| 9 X  | R16L788 の拡張機能                         |     |

| 9.1  | RTS/DTR ハードウェアフロー制御                   |     |

| 9.2  | CTS/DSR フロー制御                         |     |

| 9.3  | オート XON/XOFF フロー制御                    |     |

| 9.4  | オート RS485 ハーフデュプレクス制御                 | 44  |

| 10   | LINUX デバイスドライバ                        | 45  |

| 10.1 | インストールオプション                           | 45  |

| 10.2 | ノード                                   |     |

| 10.3 | I/O コントロール                            |     |

| 11   | 接続例                                   |     |

| **   | 1% NV I/ 3                            | I / |

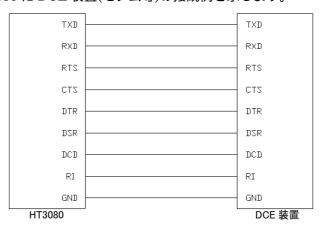

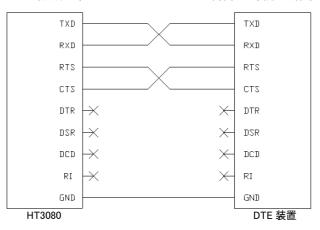

| 11.1 | RS232C モデム接続            | 47 |

|------|-------------------------|----|

| 11.2 | RS232C クロス接続            | 47 |

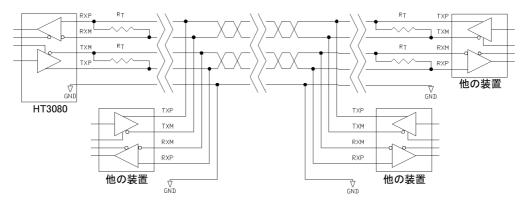

| 11.3 | RS422 機器との接続(1 対 1 の場合) | 48 |

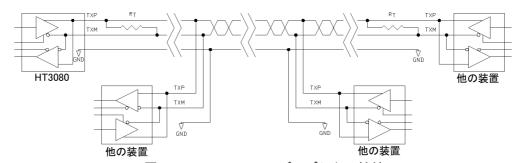

| 11.4 | RS485 ハーフデュプレクス接続       | 48 |

| 11.5 | RS485 フルデュプレクス接続        | 48 |

| 12   | ソフトウェア制作時の注意事項          | 49 |

| 12.1 | DLL/DLM 設定值             | 49 |

| 12.2 | RS485 送信ドライバ制御          | 49 |

| 12.3 | RS485 ハーフ・フルデュプレクス設定    | 49 |

| 12.4 | フロー制御機能の設定(LINUX)       | 49 |

| 12.5 | 自動フロー制御機能               | 50 |

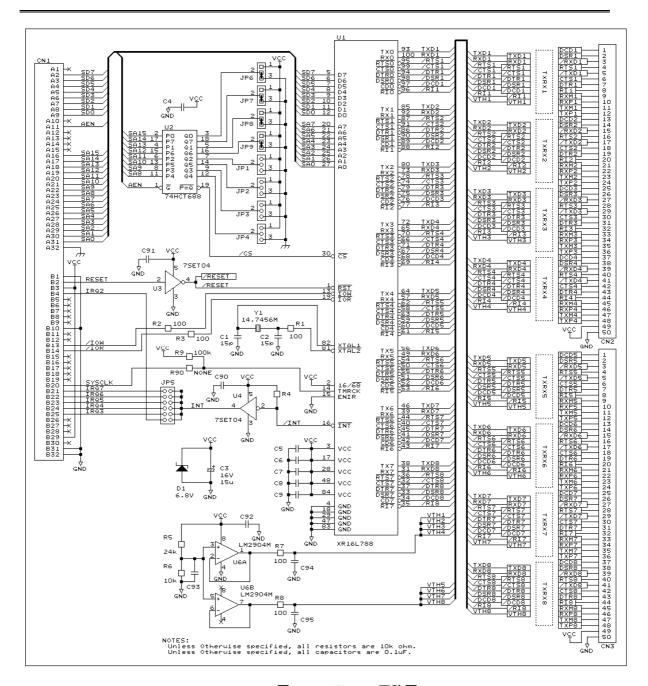

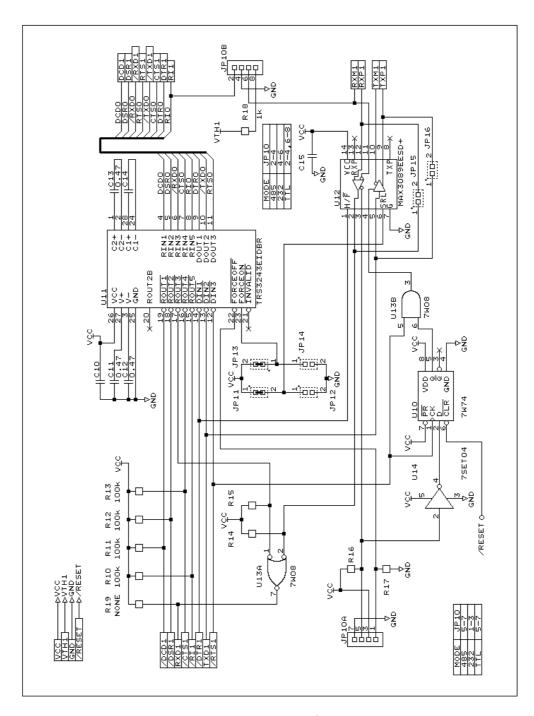

| 13   | 回路図                     | 51 |

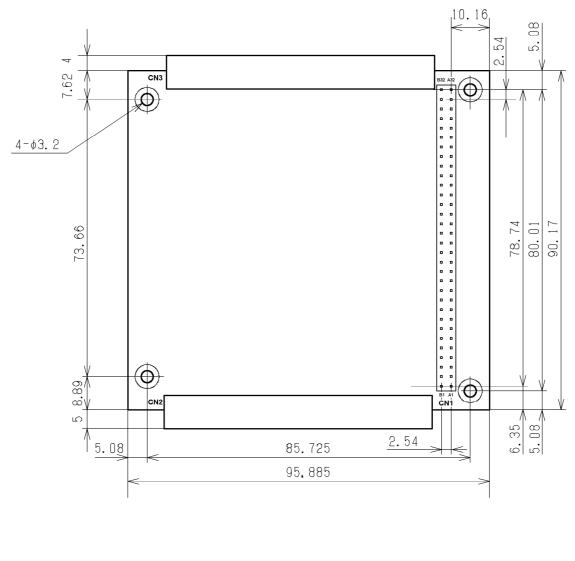

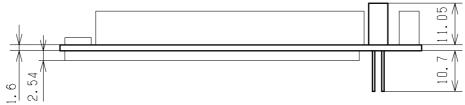

| 14   | 外形寸法図                   | 53 |

### 図目次

| 义  | 7-1 HT3080 ブロック図           | 14 |

|----|----------------------------|----|

| 図  | 7-2 各チャンネルドライバ部 ブロック図      | 15 |

| 义  | 7-3 オプションケーブル結線            | 18 |

|    | 7-4 JP5 の設定                |    |

| 义  | 7-5 JPN0 ラインドライバ選択         | 21 |

| 义  | 7-6 RS485 出力イネーブル信号の制御     | 23 |

| 义  | 8-1 XR16L788 のレジスタ概要       | 24 |

| 义  | 8-2 IER の構成                | 26 |

| 义  | 8-3 ISR の構成                | 27 |

| 义  | 8-4 FCR の構成                | 28 |

| 义  | 8-5 LCR の構成                | 29 |

| 义  | 8-6 MCR の構成                | 30 |

| 义  | 8-7 LSR の構成                | 31 |

| 义  | 8-8 MSR の構成                | 31 |

| 义  | 8-9 RS485DLY の構成           | 32 |

| 义  | 8-10 FCTR の構成              | 33 |

| 义  | 8-11 EFR の構成               | 34 |

| 义  | 8-12 XCHAR の構成             | 35 |

| 义  | 8-13 INT0 の構成              | 37 |

| 义  | 8-14 INT1~3 の構成            | 37 |

| 义  | 8-15 TIMERCTRL の構成         | 37 |

|    | 8-16 TIMERLSB/TIMERMSB の構成 |    |

| 义  | 8-17 8XMODE の構成            | 38 |

| 义  | 8-18 RESET の構成             | 39 |

| 义  | 8-19 SLEEP の構成             | 39 |

| 义  | 11-1 RS232C モデム接続          | 47 |

| 义  | 11-2 RS232C クロス接続          | 47 |

| 义  | 11-3 RS422 フルデュプレクス接続      | 48 |

| 义  | 11-4 RS485 ハーフデュプレクス接続     | 48 |

| 図  | 11-5 RS485 マルチドロップ接続       | 48 |

| 図  | 13-1 HT3080 回路図 1          | 51 |

| 义  | 13-2 HT3080 回路図 2          | 52 |

| ভা | 1/-1 HT3080 外形寸注図          | 53 |

### 表目次 表 6-1 HT3080 仕様.......13 表 7-3 CN3 信号配列.......16 表 7-5 CN2/CN3 信号......17 表 7-7 CN2/3 適合ソケット型式.......17 表 7-8 オプションケーブルコネクタ型式.......18 表 7-9 D-suB9 ピン(オス)コネクタ信号配列 .......19 表 7-10 JP1~4 の設定とベースアドレス......19 表 7-11 JP6~9 の設定とベースアドレス......20 表 7-12 JPN1/JPN2 設定とスルーレート .......21 表 7-13 JPN3/JPN4 設定とオートパワーダウン......22 表 8-2 分周比計算式.......26 表 8-4 割り込み要因とプライオリティレベル .......27 表 8-5 割り込みの発生、クリア条件.......28 表 8-6 FCR の各ビット機能.......28 表 8-7 FIFO トリガテーブルとトリガレベル設定値.......29 表 8-8 LCR の各ビット機能.......30 表 8-9 MCR の各ビット機能.......30 表 8-10 LSR の各ビット機能.......31 表 8-11 MSR の各ビット機能.......32 表 8-14 EFR の各ビット機能.......34 表 8-15 ソフトウェアフロー制御の設定 .......34 表 8-18 TIMERCTRL の各ビット機能.......38 表 9-1 RTS/DTR フロー制御を行う場合に設定するレジスタ.......42 表 9-2 CTS/DSR フロー制御を行う場合に設定するレジスタ.......42 表 9-4 オート RS485 ハーフデュプレクス制御を行う場合に設定するレジスタ....... 44 表 10-1 ドライバインストールオプション.......45 表 10-2 IOCTL コマンドとパラメータ......46

## 1 はじめに

このたびは HT3080 をお求めいただき、ありがとうございます。

HT3080 は XR16L788(EXAR)を採用した 8 ポート UART モジュールで、ジャンパ切替でポート毎に RS232C/485(422)/TTL レベルの切替ができます。

バスは 8bit の PC/104 準拠となっており、弊社 HT シリーズの CPU だけでなく、他の CPU にも容易にインターフェースすることができます。ボードの占有 I/O アドレスや使用する割り込みチャンネル選択はジャンパによって設定できます。

本マニュアルは、HT3080 の仕様や使用方法について書かれたものです。HT3080 の機能を最大限引き出すために、ご活用いただければ幸いです。

なお、本マニュアルでは XR16L788 の機能詳細については記述しておりませんので、 XR16L788 のデータシートもあわせてご参照ください。

## 2注意事項

## 2.1 安全に関する注意事項

HT3080 を安全にご使用いただくために、特に以下の点にご注意くださいますようお願いいたします。

本製品には一般電子機器用(OA機器・通信機器・計測機器・工作機械等)に製造された半導体部品を使用しておりますので、その誤作動や故障が直接生命を脅かしたり、身体・財産等に危害を及ぼす恐れのある装置(医療機器・交通機器・燃焼制御・安全装置等)に組み込んで使用しないでください。

また、半導体部品を使用した製品は、外来ノイズやサージにより誤作動したり故障したりする可能性がありますので、ご使用になる場合は万一誤作動、故障した場合においても生命・身体・財産等が侵害されることのないよう、装置としての安全設計(リミットスイッチやヒューズ・ブレーカ等の保護回路の設置、装置の多重化等)に万全を期されますようお願い申しあげます。

## 2.2 取り扱い上の注意事項

HT3080 に恒久的なダメージをあたえないよう、取り扱い時には以下のような点にご注意ください。

● 電源の投入

HT3080 や周辺回路に電源がはいっている状態では絶対に本ボードの着脱を行わないでください。

静電気

HT3080 には CMOS デバイスを使用しておりますので、ご使用になるまでは帯電防止対策のされている、出荷時のパッケージ等にて保管してください。

● ラッチアップ

電源および入出力からの過大なノイズやサージ、電源電圧の急激な変動等で使用している CMOS デバイスがラッチアップを起こす可能性があります。いったんラッチアップ状態となると、電源を切断しないかぎりこの状態が維持されるため、デバイスの破損につながることがあります。ノイズの影響を受けやすい入出力ラインには保護回路を入れることや、ノイズ源となる装置と共通の電源を使用しない等の対策をとることをお勧めします。

## 3 XR16L788 概要

HT3080 はコントローラに XR16L788(EXAR)を使用しています。 XR16L788 は 8 ポート UART で、以下のような特徴を備えています。

- 8 チャンネルで単一の割り込みを占有

- 8 チャンネル同時初期化機能

- 16C550 互換レジスタ(拡張機能を除く)

- RS485 ハーフデュプレクス自動制御

- 64 バイト送信/受信 FIFO

- プログラマブル FIFO トリガレベル

- ハードウェア自動フロー制御

- ソフトウェア自動フロー制御

- 汎用タイマカウンタ

XR16L788 の詳細な機能については、以下の資料をご参照ください。

XR16L788 Datasheet version1.2.3 July 2008 http://www.exar.com/

## 4 資料・参考文献

本マニュアル作成に際して使用した資料・参考文献を以下に示します。

- Exar XR16L788 Data Sheet version.1.2.3(2008/7 発行)

- Maxim MAX3089E Datasheet Rev.1

- TI TRS3243E Datasheet (2009/7 発行)

## 5 テストプログラム

HT3080 には、動作確認のためのテストプログラムが用意されています。このプログ ラムは C で記述されており、ソースも添付されていますので、プログラミングサンプ ルとしてもご利用いただけます。

これらのプログラムは HT3080 のテストを目的としたものであり、プログラムの正当 性および特定の用途への適合性を保証するものではありません。

## 5.1 HT1070/Armadillo-9 との組み合わせ

HT3080 のテストに HT1070 または株式会社アットマークテクノの Armadillo-9 を使 用する場合の手順を説明します。

### 5.1.1 準備

- パソコン用通信ソフトウェア ターミナルソフトが HT1070 や Armadillo-9 のコンソール用に必要です。

- シリアルポート テストに使用するパソコンには上記コンソールに使用するシリアルポートと、 HT3080 の 1 チャンネル分の最低 2 ポートが必要です。 別々の PC2 台でもかまい ません。

- ネットワーク設定

- HT1070/Armadillo-9 に FTP でファイル転送して実行する場合、 HT1070/Armadillo-9 と PC とが通信可能なネットワークに接続されている必要 があります。

- HT3080 のジャンパ設定

#### JP1 ~ 4

JP5

テストプログラムは、ボードの I/O ベースアドレスが 0500H であることを仮定し ていますので、JP1=0, JP2=1, JP3=0, JP4=1 に設定してください。

テストプログラムでは IRQ4 を使用します。設定については7.3.2項をご参照くだ さい。

### JP10,JP20,JP30,JP40,JP50,JP60,JP70,JP80

5.1.2項のテストプログラムでは RS232C モードとなるように、5.1.3項のテスト プログラムでは RS485 モードとなるように設定してください。設定については 7.3.4項をご参照ください。

テストプログラムの HT1070/Armadillo-9 への転送

ドライバとサンプルプログラムは tgz 圧縮されています。FTP 経由で HT1070/Armadillo-9 に転送するか、コンパクトフラッシュに保存して実行する ことができます。ここでは FTP 経由で転送する方法を説明します。

Armadillo-9 の場合、ftp 転送で使用するエリアをあらかじめ大きくしておく必要

#### があります。Armadillo-9 のコンソールで

mount -t tmpfs tmpfs /home/ftp/pub

と入力してください。

PC 側から転送するための FTP コマンドの例を示します。

#ftp 192.168.1.10 (HT1070/Armadillo-9 の IP アドレスを指定)

Connected to 192.168.1.10.

220 armadillo FTP server (Version 6.4/OpenBSD/Linux-ftpd-0.17) ready.

User (192.168.1.10:(none)): ftp (ログイン名は ftp)

331 Guest login ok, type your name as password.

Password: (パスワードも ftp)

230 Guest login ok, access restrictions apply.

ftp> cd pub (pub ディレクトリに移動)

250 CWD command successful.

ftp> bin (バイナリモードに変更)

200 Type set to I.

ftp> put 3080test232.ht1070.2421.tgz (転送するファイルを put コマンドで転送)

200 PORT command successful.

150 Opening BINARY mode data connection for 'ht3080.k2421.test.tar.gz'

226 Transfer complete.

ftp: 14350 bytes sent in 0.00Seconds 14350000.00Kbytes/sec.

ftp> quit (FTP プログラムを終了)

221 Goodbye.

HT1070/Armadillo-9 のネットワークアドレスは ifconfig コマンドで確認してください。

### 5.1.2 RS232C 送受信テスト

● プログラムファイル名

3080test232.ht1070.2416.tgz (HT1070 kernel2.4.16 用) 3080test232.ht1070.2421.tgz (HT1070 kernel2.4.21 用) 3080test232.a9.2612.tgz (Armadillo-9 kernel2.6.12 用)

● 動作概要

HT3080 の全チャンネルを 9600bps で初期化し、改行で区切られた各チャンネル の受信内容をコンソールに表示します。また受信した文字列を逆順にした文字列をそのチャンネルに返信します。いずれかのチャンネルで"stop"と入力されると プログラムは終了します。起動時のオプションでハードフロー制御、ソフトフロー制御を指定することができます。

- 操作手順

- 1. プログラムの転送

FTP でプログラムファイルを転送します。(5.1.1項参照) 転送したファイルをHT1070/Armadillo-9 のコンソールからコマンドで解凍してください。

#cd /home/ftp/pub

#tar xzf 3080test232.ht1070.2416.tgz (転送ファイル名、例ではHT1070の kernel2.4.16 用)

2. デバイスノードの作成とドライバのインストール

解凍された start.sh を実行し、デバイスノード作成とデバイスドライバのインストールを行います。

#./start.sh

### 3. アプリケーションの実行

3080test232 を実行すると起動メッセージが表示され、各チャンネルからの入力内容が表示されます。

# ./test232

HT3080 Send/Receive sample

Received CH1:test message

Received CH3:ht3080 8ch UART

Received CH3:stop

#

各チャンネルから入力してもコンソールに受信データが表示されない....

● ボーレートの確認

各チャンネルは 9600bps に初期化されます。HT3080 に接続しているシリアルポートの通信速度を確認してください。

● JP 設定状態の確認

I/O ベースアドレスが正しく設定されていなかったり、割り込みチャンネルの設定が誤っていると動作しません。また各チャンネルで使用するドライバが 232C に設定されていない場合も動作しません。

### 5.1.3 RS485 送受信テスト

● プログラムファイル名

3080test485.ht1070.2416.tgz 3080test485.ht1070.2421.tgz

3080test485.a9.2612.tgz

(HT1070 kernel2.4.16 用)

(HT1070 kernel2.4.21 用)

(Armadillo-9 kernel2.6.12 用)

● 準備

ジャンパ JPx0 でテストに使用するチャンネルを RS485 に設定します。テストではチャンネル 1 を RS485 のデータ送信に使用しますので、チャンネル 1 の送信信号を受信するチャンネルに接続します。

例えばチャンネル4をフルデュプレクス接続で使用する場合、

TxP1(CN2-12) - RxP4(CN2-46)

TxM1(CN2-11) - RxM4(CN2-45)

を接続します。

チャンネル4をハーフデュプレクス接続で使用する場合は、

TxP1(CN2-12) - TxP4(CN2-48)

TxM1(CN2-11) - TxM4(CN2-47)

を接続します。

#### ● 動作概要

HT3080 の全チャンネルを 9600bps で初期化し、各チャンネルの受信待ち状態でプログラムを常駐させます。ここでコンソールから echo コマンドを使い送信データをチャンネル 1 に送信すると、接続された受信チャンネルでの受信内容がコンソールに表示されます。送信データとして"stop"を送信すると、プログラムは終了します。起動時のオプションでフルデュプレクス、ハーフデュプレクスを指定することができます。なお自動 RS485 ハーフデュプレクス機能が有効となっているため、フルデュプレクス設定の場合でも送信中以外は送信ドライバがオフとなります。

### ● 操作手順

#### 1. プログラムの転送

FTP でプログラムファイルを転送します。(5.1.1項参照) 転送したファイルをHT1070/Armadillo-9 のコンソールからコマンドで解凍してください。

#cd /home/ftp/pub

#tar xzf 3080test485.ht1070.2416.tgz (転送ファイル名、例ではHT1070の kernel2.4.16用)

2. デバイスノードの作成とドライバのインストール

解凍された start.sh を実行し、デバイスノード作成とデバイスドライバのインストールを行います。

#./start.sh

### 3. アプリケーションの実行

3080test485 を実行します。このとき、このプログラムを常駐させるために行末には&をつけて起動してください。コンソールには起動メッセージが表示されますが、Enter キーを押すとプロンプトに戻ります。

# ./test485 &

HT3080 RS485 Receive sample

#

ここで、echo コマンドを使い、チャンネル 1 に文字列を送信すると、受信チャンネルで受信された内容がコンソールに表示されます。

# echo test message >/dev/ttyXR78x0

Received CH1:test message

#

起動時にオプション -full を指定すると、フルデュプレクス制御を、-half を指定するとハーフデュプレクス制御を行います。

送信データがコンソールに表示されない....

### ● JP 設定状態の確認

I/O ベースアドレスが正しく設定されていなかったり、割り込みチャンネルの設定が誤っていると動作しません。また各チャンネルで使用するドライバがRS485に設定されていない場合も動作しません。

● 接続する信号

ハーフデュプレクスの場合、信号の送受信に使用する信号は TXPn と TXMn です。また信号には極性がありますので各チャンネルの非反転信号同士、反転信号同士を接続してください。他の機器を接続する場合、信号の極性が A/B で表示されていることがありますが、デバイスメーカによって極性の割り当てが異なるため注意が必要です。

## 5.2 HT1030/HT1040 との組み合わせ

HT3080 のテストに HT1030 または HT1040 を使用する場合の手順を説明します。

### 5.2.1 準備

- パソコン用通信ソフトウェア

- ターミナルソフトが HT1030 や HT1040 のコンソール接続用に必要です。

- シリアルポート

テストに使用するパソコンには上記コンソールに使用するシリアルポートと、HT3080 の 1 チャンネル分の最低 2 ポートが必要です。 別々の PC2 台でもかまいません。

● HT3080 のジャンパ設定

### JP1 ~ 4

テストプログラムは、ボードの I/O ベースアドレスが 0500H であることを仮定していますので、JP1=0, JP2=1, JP3=0, JP4=1 に設定してください。

#### JP5

テストプログラムでは IRQ4 を使用します。設定については7.3.2項をご参照ください。

#### JP10,JP20,JP30,JP40,JP50,JP60,JP70,JP80

5.1.2項のテストプログラムでは RS232C モードとなるように、5.1.3項のテストプログラムでは RS485 モードとなるように設定してください。設定については7.3.4項をご参照ください。

#### テストプログラムの実行方法

サンプルプログラムは HT1030/HT1040 の S ファイルローダを使って RAM に転送して実行するファイル、フラッシュメモリに書き込みして実行するファイルの 2 種類を用意しています。S ファイルローダを使用する場合は転送後 G コマンドを使用して 400000 番地から実行してください。なおフラッシュメモリに書き込みするテストプログラムのコンソール通信速度は 38400bps です。

### 5.2.2 RS232C 送受信テスト

● プログラムファイル名

3080test232Loader.s (S ファイルローダ用) 3080test232Flash.s (フラッシュメモリ書き込み用)

● 動作概要

HT3080 の全チャンネルを 9600bps で初期化し、改行で区切られた各チャンネルの受信内容をコンソールに表示します。また受信した文字列を逆順にした文字列をそのチャンネルに返信します。起動時にハードフロー制御、ソフトフロー制御を指定することができます。

● 操作手順

S ファイルローダを使用する場合のコンソール表示例を示します。プログラムを 転送して実行後、この例ではチャンネル 1 に接続されたポートから hello(+Enter キー)と入力しています。コンソールに表示されるのと同時に、チャンネル 1 には olleh の文字列が返信されます。 - L (コマンド投入後ターミナルソフトのファイル転送機能で 3080 test 232 Loader . s を転送) - G400000

HT3080 RS232C Send/Receive sample

Received strings from CH1-8 are shown on the console.

Received CH1:hello

各チャンネルから入力してもコンソールに受信データが表示されない....

● ボーレートの確認

各チャンネルは 9600bps に初期化されます。HT3080 に接続しているシリアルポートの通信速度を確認してください。

● JP 設定状態の確認

I/O ベースアドレスが正しく設定されていなかったり、割り込みチャンネルの設定が誤っていると動作しません。また各チャンネルで使用するドライバが 232C に設定されていない場合も動作しません。

## 5.2.3 RS232C フロー制御受信テスト

● プログラムファイル名

3080flowtest232Loader.s 3080flowtest232Flash.s (S ファイルローダ用) (フラッシュメモリ書き込み用)

● 動作概要

HT3080 のチャンネル 1 を 115.2kbps で初期化し、受信内容をコンソールに表示します。起動時にハードフロー制御、ソフトフロー制御を指定することができます。

● 操作手順

S ファイルローダを使用する場合のコンソール表示例を示します。プログラムを転送して実行するとソフトウェアフロー制御またはハードウェアフロー制御を行うか確認するメッセージが表示され、いずれかに Y を入力すると該当するフロー制御の設定で動作します。いずれも N を入力するとフロー制御を行わない設定で動作します。この例ではハードウェアフロー制御を選択し、その後チャンネル 1 に接続されたポートから hello と入力しています。チャンネル 1 に接続した PCのターミナルソフトでテキストファイル送信を行うと、送信したファイル内容がHT1030/1040のコンソールに表示されます。チャンネル 1 の受信速度(115.2kbps)はコンソールの表示速度(HT1030では9600bps,HT1040では38400bps)よりも速いですが、フロー制御が働き、コンソールには受信データが欠落なく表示されます。(ターミナルソフトは該当するフロー制御機能を有効に設定してください。)

-L (コマンド投入後ターミナルソフトのファイル転送機能で3080flowtest232Loader.sを転送)

-G400000

HT3080 RS232C Flow Control Test

Use Software Flow Control?(Y/N):n

Use Hardware Flow Control?(Y/N):v

Hardware flow control mode

Received characters from CH1 are shown on the console.

hello

コンソールに受信データが表示されない....

● ボーレートの確認

チャンネル 1 は 115.2kbps に初期化されます。HT3080 に接続しているシリアルポートの通信速度を確認してください。

● JP 設定状態の確認

I/O ベースアドレスが正しく設定されていなかったり、割り込みチャンネルの設定が誤っていると動作しません。また各チャンネルで使用するドライバが 232C に設定されていない場合も動作しません。

ハードウェアフロー制御ラインのレベルをモニタしても、フロー制御が機能している 状態が確認できない....

ソフトウェアフロー制御のコードが送られているかモニタしてもフロー制御のキャラクタが送られていることが確認できない....

● チャンネル 1 に接続したターミナルからのデータ送信間隔が長い場合、フロー制御が動作する条件が成立せず、フロー制御を行わずに受信できる場合があります。(たとえば通信速度が 115kbps でもデータ送信間隔が 1ms 程度の場合、実質9600bps 相当となってしまいます。)

コンソールに表示される内容が一部欠落している....

● チャンネル 1 に接続した PC で使用しているターミナルソフトの、フロー制御設 定が正しいか確認してください。

### 5.2.4 RS485 送受信テスト

● プログラムファイル名

3080test485Loader.s 3080test485Flash.s (S ファイルローダ用) (フラッシュメモリ書き込み用)

● 準備

ジャンパ JPx0 でテストに使用するチャンネルを RS485 に設定します。テストではチャンネル 1 を RS485 のデータ送信に使用しますので、チャンネル 1 の送信信号を受信するチャンネルに接続します。

例えばチャンネル 4 をフルデュプレクス接続で使用する場合、

TxP1(CN2-12) - RxP4(CN2-46)

TxM1(CN2-11) - RxM4(CN2-45)

を接続します。

チャンネル4をハーフデュプレクス接続で使用する場合は、

TxP1(CN2-12) - TxP4(CN2-48)

TxM1(CN2-11) - TxM4(CN2-47)

を接続します。

#### ● 動作概要

HT3080 の全チャンネルを 9600bps で初期化し、各チャンネルの受信待ち状態となります。ここでコンソールからテキストを入力し Enter を押すと、チャンネル1 から入力されたテキストが送信されます。接続された受信チャンネルでの受信データがあると、内容がコンソールに表示されます。起動時にフルデュプレクス、ハーフデュプレクスを指定することができます。

### ● 操作手順

S ファイルローダを使用する場合のコンソール表示例を示します。プログラムを転送して実行後、この例ではハーフデュプレクスを選択し、コンソールからhello(+Enter キー)と入力してチャンネル 1 からテキストを送信しています。送信したデータが表示された後、接続先のチャンネルで受信されたデータがコンソールに表示されています。

-L (コマンド投入後ターミナルソフトのファイル転送機能で 3080 test 485 Loader.s を転送) - G400000

HT3080 RS485 Send/Receive sample Use Half Duplex interface?(Y/N):*y*

Half Duplex mode

Enter string to send from CH1 then press Enter

(Typed characters are not echoed back.)

Send CH1>hello (入力文字はエコーバックしないが送信後に内容が表示される)

Recv CH1:hello

Recv CH4:hello

この例ではチャンネル 1 と 4 がハーフデュプレクス接続されており、送信したデータは送信したチャンネルでも受信されるため、チャンネル 1 と 4 で受信データが表示されています。

起動時ハーフデュプレクス接続か確認するメッセージが表示され、Y を入力する とハーフデュプレクス、それ以外の場合はフルデュプレクスの設定で動作します。

送信データがコンソールに表示されない....

### ● JP 設定状態の確認

I/O ベースアドレスが正しく設定されていなかったり、割り込みチャンネルの設定が誤っていると動作しません。また各チャンネルで使用するドライバがRS485 に設定されていない場合も動作しません。

### ● 接続する信号

ハーフデュプレクスの場合、信号の送受信に使用する信号は TXPn と TXMn です。また信号には極性がありますので各チャンネルの非反転信号どうし、反転信号どうしを接続してください。他の機器を接続する場合、信号の極性が A/B で表示されていることがありますが、デバイスメーカによって極性の割り当てが異なるため注意が必要です。

## 6 仕様

表 6-1に HT3080 の仕様を示します。

### 表 6-1 HT3080 仕様

| コントローラ        | XR16L788(Exar)                |  |  |

|---------------|-------------------------------|--|--|

| RS232C ドライバ素子 | TRS3243E(TI または相当品)           |  |  |

| RS485 ドライバ素子  | MAX3089E(Maxim)               |  |  |

| I/O アドレス      | A[8:11]をジャンパで選択、100h 毎に設定可能   |  |  |

|               | 144 バイトを占有                    |  |  |

| チャンネル数        | 8                             |  |  |

| ボーレートジェネレータ   | 各チャンネル独立、コントローラ内蔵             |  |  |

|               | RS232C:230.4kbps max.         |  |  |

|               | RS485/422/TTL: 460.8kbps max. |  |  |

| 割り込み          | 全チャンネルで 1 つの割り込みを共有           |  |  |

|               | IRQ2 から 7 をジャンパで選択            |  |  |

| 基板サイズ         | 90.2×95.9×15.2mm ( 突出部を含まず )  |  |  |

| 電源電圧          | 5V ± 5% 20mA max.             |  |  |

|               | (周辺回路無接続時の typ.値)             |  |  |

| 動作温度範囲        | -20 ~ 70                      |  |  |

## 7ハードウェア機能

この章では、HT3080のハードウェア機能に関連する事項について説明します。なお、XR16L788の詳細についてはデータシートをご参照ください。

## 7.1 ブロック図

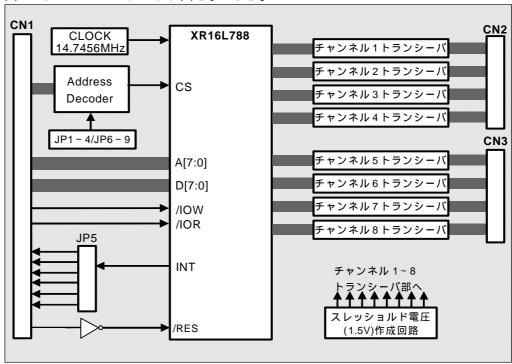

図 7-1に HT3080 のブロック図を示します。

図 7-1 HT3080 ブロック図

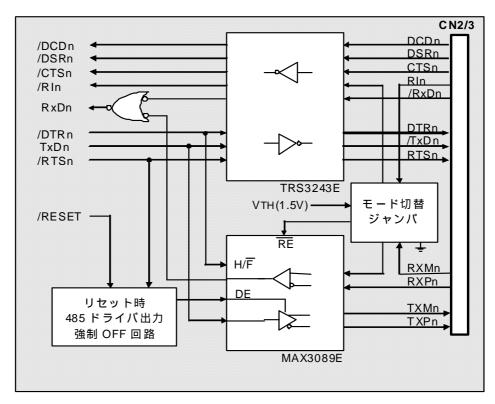

各チャンネルのトランシーバ回路ブロックを図 7-2に示します。信号名の n は、チャンネル番号  $1 \sim 8$  を表わしています。

図 7-2 各チャンネルドライバ部 ブロック図

## 7.2 コネクタ信号配置・機能

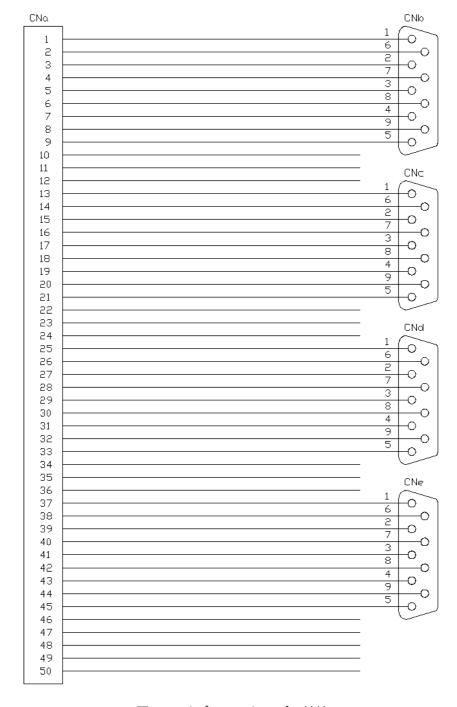

## 7.2.1 HT3080 コネクタピン配列

表 7-1から表 7-3にコネクタの信号配列を示します。表中、-印の端子は未使用です。

表 7-1 CN1 信号配列

| A1  | -   | B1  | GND      |

|-----|-----|-----|----------|

| A2  | SD7 | B2  | RESETDRV |

| А3  | SD6 | В3  | +5V      |

| A4  | SD5 | В4  | IRQ2     |

| A5  | SD4 | B5  | -        |

| A6  | SD3 | В6  | -        |

| A7  | SD2 | В7  | -        |

| A8  | SD1 | B8  | -        |

| A9  | SD0 | В9  | -        |

| A10 | -   | B10 | GND      |

| A11 | AEN | B11 | -        |

| A12 | 1   | B12 | -        |

| A13 |     | B13 | /IOW     |

| A14 | -   | B14 | /IOR     |

| A15 | -   | B15 | -        |

| SA15 | B16                                                         | -                                                                                                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                             |                                                                                                                                                                                                                                                                                                                 |

| SA14 | B17                                                         | -                                                                                                                                                                                                                                                                                                               |

| SA13 | B18                                                         | -                                                                                                                                                                                                                                                                                                               |

| SA12 | B19                                                         | -                                                                                                                                                                                                                                                                                                               |

| SA11 | B20                                                         | SYSCLK                                                                                                                                                                                                                                                                                                          |

| SA10 | B21                                                         | IRQ7                                                                                                                                                                                                                                                                                                            |

| SA9  | B22                                                         | IRQ6                                                                                                                                                                                                                                                                                                            |

| SA8  | B23                                                         | IRQ5                                                                                                                                                                                                                                                                                                            |

| SA7  | B24                                                         | IRQ4                                                                                                                                                                                                                                                                                                            |

| SA6  | B25                                                         | IRQ3                                                                                                                                                                                                                                                                                                            |

| SA5  | B26                                                         | -                                                                                                                                                                                                                                                                                                               |

| SA4  | B27                                                         | 1                                                                                                                                                                                                                                                                                                               |

| SA3  | B28                                                         | -                                                                                                                                                                                                                                                                                                               |

| SA2  | B29                                                         | +5V                                                                                                                                                                                                                                                                                                             |

| SA1  | B30                                                         | 1                                                                                                                                                                                                                                                                                                               |

| SA0  | B31                                                         | GND                                                                                                                                                                                                                                                                                                             |

| GND  | B32                                                         | GND                                                                                                                                                                                                                                                                                                             |

|      | SA13 SA12 SA11 SA10 SA9 SA8 SA7 SA6 SA5 SA4 SA3 SA2 SA1 SA0 | SA13       B18         SA12       B19         SA11       B20         SA10       B21         SA9       B22         SA8       B23         SA7       B24         SA6       B25         SA5       B26         SA4       B27         SA3       B28         SA2       B29         SA1       B30         SA0       B31 |

表 7-2 CN2 信号配列

表 7-3 CN3 信号配列

| 1  | DCD1               | 2  | DSR1              |

|----|--------------------|----|-------------------|

| 3  | /RXD1              | 4  | RTS1              |

| 5  | /TXD1              | 6  | CTS1              |

| 7  | DTR1               | 8  | RI1 <sup>*1</sup> |

| 9  | RXM1 <sup>*2</sup> | 10 | RXP1              |

| 11 | TXM1               | 12 | TXP1              |

| 13 | DCD2               | 14 | DSR2              |

| 15 | /RXD2              | 16 | RTS2              |

| 17 | /TXD2              | 18 | CTS2              |

| 19 | DTR2               | 20 | RI2 <sup>*1</sup> |

| 21 | RXM2 <sup>*2</sup> | 22 | RXP2              |

| 23 | TXM2               | 24 | TXP2              |

| 25 | DCD3               | 26 | DSR3              |

| 27 | /RXD3              | 28 | RTS3              |

| 29 | /TXD3              | 30 | CTS3              |

| 31 | DTR3               | 32 | RI3 <sup>*1</sup> |

| 33 | RXM3 <sup>*2</sup> | 34 | RXP3              |

| 35 | TXM3               | 36 | TXP3              |

| 37 | DCD4               | 38 | DSR4              |

| 39 | /RXD4              | 40 | RTS4              |

| 41 | /TXD4              | 42 | CTS4              |

| 43 | DTR4               | 44 | RI4 <sup>*1</sup> |

| 45 | RXM4 <sup>*2</sup> | 46 | RXP4              |

| 47 | TXM4               | 48 | TXP4              |

| 49 | +5V                | 50 | GND               |

| 1 DCD5 3 /RXD5 5 /TXD5 |      | DSR5              |  |

|------------------------|------|-------------------|--|

| ,,,,,,                 | 5 4  | DTCE              |  |

| 5 /TXD5                |      | RTS5              |  |

|                        | 6    | CTS5              |  |

| 7 DTR5                 | 8    | RI5 <sup>*1</sup> |  |

| 9 RXM5                 | 10   | RXP5              |  |

| 11 TXM5                | 12   | TXP5              |  |

| 13 DCD6                | 14   | DSR6              |  |

| 15 /RXD6               | 6 16 | RTS6              |  |

| 17 /TXD6               | 18   | CTS6              |  |

| 19 DTR6                | 20   | RI6 <sup>*1</sup> |  |

| 21 RXM6                | 22   | RXP6              |  |

| 23 TXM6                | 24   | TXP6              |  |

| 25 DCD7                | 26   | DSR7              |  |

| 27 /RXD7               | 7 28 | RTS7              |  |

| 29 /TXD7               | 30   | CTS7              |  |

| 31 DTR7                | 32   | RI7 <sup>*1</sup> |  |

| 33 RXM7                | 34   | RXP7              |  |

| 35 TXM7                | 36   | TXP7              |  |

| 37 DCD8                | 38   | DSR8              |  |

| 39 /RXD8               | 3 40 | RTS8              |  |

| 41 /TXD8               | 3 42 | CTS8              |  |

| 43 DTR8                | 44   | RI8 <sup>*1</sup> |  |

| 45 RXM8                | 46   | RXP8              |  |

| 47 TXM8                | 48   | TXP8              |  |

| 49 +5V                 | 50   | GND               |  |

<sup>\*1: 485</sup> モード,TTL モードでは GND と \*2:232C モードでは GND となります。 なります。

## 7.2.2 バス信号(CN1)

CN1 には、CPU バス信号が配置されています。信号配置は PC/104 に準拠しています。 表 7-4 CN1 信号

| 信号名      | 機能                                                                 |

|----------|--------------------------------------------------------------------|

| SA[15:0] | アドレス入力です。                                                          |

| AEN      | アドレス入力が有効であることを示します。I/O のアドレスデコードには SA とともに、この信号が L であることを使用しています。 |

| SD[7:0]  | データ入出力バスです。                                                        |

| /IOR     | 1/0 リード信号です。                                                       |

| /IOW     | 1/0 ライト信号です。                                                       |

| RESETDRV | リセット入力です。Hアクティブですのでご注意ください。                                        |

| IRQ[7:2] | 外部割り込み出力です。本ボードが使用する割り込み出力は JP5 で選択します。                            |

| +5V      | システムの電源です。+5V を供給します。                                              |

| GND      | システムの GND です。                                                      |

## 7.2.3 入出力信号(CN2/CN3)

CN2、CN3 にはシリアル入出力信号が配置されています。表 7-5に各信号の機能を示します。(表中信号名の n はチャンネル番号  $1\sim8$  を表しています。) RIn および RXMn は使用するモードによって GND となります。RS485 信号をハーフデュプレクスで使用する場合は、TxPn および TxMn を使用してください。

表 7-5 CN2/CN3 信号

| 信号名   | 入出力  | 232C      | 485 フル                         | 485 ハーフ          | TTL      |  |

|-------|------|-----------|--------------------------------|------------------|----------|--|

| /TXDn | 出力   | TxD(232C) |                                | 使用できません          |          |  |

| /RXDn | 入力   | RxD(232C) |                                | 使用できません          |          |  |

| DCDn  | 入力   | DCD(232C) |                                | 使用できません          |          |  |

| DSRn  | 入力   | DSR(232C) |                                | 使用できません          | _        |  |

| RTSn  | 出力   | RTS(232C) |                                | 使用できません          |          |  |

| CTSn  | 入力   | CTS(232C) | 使用できません                        |                  |          |  |

| DTRn  | 出力   | DTR(232C) | <br>使用できません                    |                  |          |  |

| RIn   | 入力   | RI(232C)  | G                              | ND               | GND      |  |

| RXPn  | 入力   | 使用できません   | RXP(485)                       | 使用できません          | RxD(TTL) |  |

| RXMn  | 入力   | GND       | RXM(485)                       | RXM(485) 使用できません |          |  |

| TXPn  | 出力*1 | 使用できません   | TXP(485) TXP 入出力(485) TxD(TTL) |                  |          |  |

| TXMn  | 出力*1 | 使用できません   | TXM(485) TXM 入出力(485) 使用できません  |                  |          |  |

| +5V   | -    |           | +5V                            |                  |          |  |

| GND   | -    |           | GND                            |                  |          |  |

<sup>\*1:485</sup> ハーフデュプレクス時には入出力信号となります。

### 7.2.4 コネクタ型式

コネクタの型式等を表 7-6に示します。コネクタのメーカ・型式は同等他社製品が使用される場合があります。

表 7-6 コネクタ型式

| コネクタ | メーカ    | <b>大</b> 型       | 備考                    |

|------|--------|------------------|-----------------------|

| CN1  | ASTRON | 25-0206-232-1G-R | PC/104 J1 スタックスルーコネクタ |

| CN2  | ASTRON | 26-02-225-1G-R   | 50 極ボックスピンヘッダ         |

| CN3  | ASTRON | 26-02-225-1G-R   | 50 極ボックスピンヘッダ         |

CN2、CN3 に適合するソケットの参考型式を表 7-7に示します。

表 7-7 CN2/3 適合ソケット型式

| メーカ   | 型式               | 備考                       |

|-------|------------------|--------------------------|

| ヒロセ電機 | HIF3BB-50D-2.54R |                          |

|       | HIF3BB-50D-2.54C | バラ線圧接タイプハウジング            |

|       | HIF3-2226SCA     | 上記ハウジング用端子(AWG#22~26)    |

| オムロン  | XG4M-5030        | ストレインリリーフ別売 型名 XG4T-5004 |

| 和泉電気  | JE1S-501         | ストレインリリーフなし品は JE1S-503   |

## 7.2.5 オプションケーブル HT3080-01

オプションケーブルは、CN2(CN3)の信号を DTE 配列の RS232C 用 Dsub9 ピンオスコネクタ 4 つに変換します。ケーブル長は約  $25 \mathrm{cm}$  です。使用部品を表 7-8に示します。コネクタのメーカ・型式は同等他社製品が使用される場合があります。

表 7-8 オプションケーブルコネクタ型式

| コネクタ  | メーカー     | <b>大</b> 型       | 備考                      |

|-------|----------|------------------|-------------------------|

| CNa   | HIROSE   | HIF3BB-50D-2.54R | 50 極圧接コネクタ              |

| CNb∼e | Amphenol | L17DEFRA09P      | 9 極 D-SUB オスピンコネクタ(IDC) |

D-SUB 取付用スペーサ、ナット、ワッシャ、ばねワッシャが4組付属します。

図 7-3にケーブルの結線を示します。

図 7-3 オプションケーブル結線

Dsub9 ピン(オス)コネクタの信号配列を表 7-9に示します。

表 7-9 D-sub9 ピン(オス)コネクタ信号配列

| ピン番号 | 機能  |

|------|-----|

| 1    | DCD |

| 2    | RXD |

| 3    | TXD |

| 4    | DTR |

| 5    | GND |

| ピン番号 | 機能  |

|------|-----|

| 6    | DSR |

| 7    | RTS |

| 8    | CTS |

| 9    | RI  |

## 7.3 ジャンパ設定

HT3080 には全チャンネルに共通の JP1~9 までのジャンパと、各チャンネル毎に JPn0 から n6 までのジャンパ(n=1~8)があります。 **出荷時 JP1~5 および JPn0(n=1~8)にはジャンパソケットが取り付けられていません**ので、使用環境にあわせて設定 してください。

### 7.3.1 JP1~JP4

JP1~4 は、本ボードの占有する 144 バイト I/O 空間の先頭アドレス(ベースアドレス) を設定します。アドレスの設定は SA[11:8]について行い、アドレスの下位 8 ビット SA[7:0]はボード内の I/O 選択に使用されるため設定することはできません。 JP1~4 は 3 極ジャンパポストで、 印の側にジャンパソケットを取り付けると 1、反対側に取り付けると 0 が設定されます。

JP の設定とベースアドレスの関係は表 7-10をご参照ください。z は JP6 ~ 9 で指定され、出荷時の設定は z=0(SA[15:12]は全て 0)となっています。JP6 ~ 9 の設定については表 7-11をご参照ください。

表 7-10 JP1~4 の設定とベースアドレス

| JP1         | IP2  | JP3 | IP4  | ベースアドレス |

|-------------|------|-----|------|---------|

| <del></del> | 01 2 | 010 | 01.1 | 170177  |

| 0           | 0    | 0   | 0    | z000    |

| 0           | 0    | 0   | 1    | z100    |

| 0           | 0    | 1   | 0    | z200    |

| 0           | 0    | 1   | 1    | z300    |

| 0           | 1    | 0   | 0    | z400    |

| 0           | 1    | 0   | 1    | z500    |

| 0           | 1    | 1   | 0    | z600    |

| 0           | 1    | 1   | 1    | z700    |

#### 《注意》

JP1~4 **のジャンパソケットは必ず設定してください。**ジャンパソケットをはずした状態で動作させないでください。

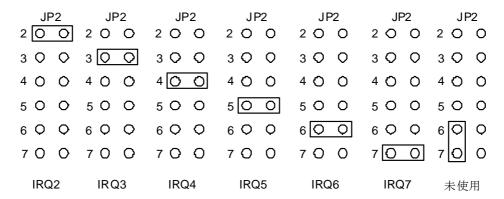

### 7.3.2 JP5

JP2 は使用する割り込みチャンネルを選択します。ジャンパソケットの設定は、図 7-4 をご参照ください。

割り込みを使用しない場合は、JP5 にジャンパソケットを取り付けしないか、図中の未使用の位置に取り付けてください。

図 7-4 JP5 の設定

### 7.3.3 JP6~9

JP6~9 は HT3080 のベースアドレス SA[15:12]を設定するジャンパで、0 チップ抵抗取り付け位置で設定します。ジャンパ番号は(数字のみで)シルク表示されています。

印のある側にチップ抵抗を取り付けた場合は 1、反対側に取り付けた場合は 0 となります。HT3080 出荷時は全て 0 に設定されています。表 7-11に JP6~9 の設定とベースアドレスの関係を示します。x は JP1~4 で指定されます。JP1~4 の設定については表 7-10をご参照ください。

| 表 | 7-11 | JP6 ~ | 9 | の設定とべっ | ・スア | ド | レス |

|---|------|-------|---|--------|-----|---|----|

|---|------|-------|---|--------|-----|---|----|

| JP6 | JP7 | JP8 | JP9 | ベースアドレス |

|-----|-----|-----|-----|---------|

| 0   | 0   | 0   | 0   | 0x00    |

| 0   | 0   | 0   | 1   | 1x00    |

| 0   | 0   | 1   | 0   | 2x00    |

| 0   | 0   | 1   | 1   | 3x00    |

| 0   | 1   | 0   | 0   | 4x00    |

| 0   | 1   | 0   | 1   | 5x00    |

| 0   | 1   | 1   | 0   | 6x00    |

| 0   | 1   | 1   | 1   | 7x00    |

| JP6 | JP7                        | JP8                                           | JP9                                                         | ベースアドレス                                                                                                                                                                         |

|-----|----------------------------|-----------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0                          | 0                                             | 0                                                           | 8x00                                                                                                                                                                            |

| 1   | 0                          | 0                                             | 1                                                           | 9x00                                                                                                                                                                            |

| 1   | 0                          | 1                                             | 0                                                           | Ax00                                                                                                                                                                            |

| 1   | 0                          | 1                                             | 1                                                           | Bx00                                                                                                                                                                            |

| 1   | 1                          | 0                                             | 0                                                           | Cx00                                                                                                                                                                            |

| 1   | 1                          | 0                                             | 1                                                           | Dx00                                                                                                                                                                            |

| 1   | 1                          | 1                                             | 0                                                           | Ex00                                                                                                                                                                            |

| 1   | 1                          | 1                                             | 1                                                           | Fx00                                                                                                                                                                            |

|     | 1<br>1<br>1<br>1<br>1<br>1 | 1 0<br>1 0<br>1 0<br>1 0<br>1 1<br>1 1<br>1 1 | 1 0 0<br>1 0 0<br>1 0 1<br>1 0 1<br>1 1 0<br>1 1 0<br>1 1 1 | 1     0     0     0       1     0     0     1       1     0     1     0       1     0     1     1       1     1     0     0       1     1     0     1       1     1     1     0 |

#### 《注意》

JP6~9 のジャンパは必ず 0 か 1 を設定してください。ジャンパをはずした状態で動作させないでください。

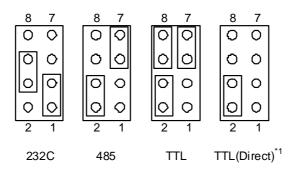

### 7.3.4 JPn0

JPn0( $n=1 \sim 8$ )は各チャンネルの送受信に使用するドライバを RS232C/485(422)/TTL から選択するジャンパです。n はチャンネル番号に対応します。設定は図 7-5をご参照ください。使用しないチャンネルの設定はいずれの状態でもかまいませんが、全てのジャンパをはずした状態でドライバの消費電力が最小となります。

図 7-5 JPn0 ラインドライバ選択

\*1:この設定で使用する場合は、JPn5 を ON にする必要があります。7.3.7項をご参照ください。

### 《注意》

図に示されていない組み合わせのジャンパ設定はしないようご注意ください。電源がジャンパで短絡される組み合わせがあり、HT3080 のパターン焼損等の事故につながる可能性があります。

### 7.3.5 JPn1/JPn2

JPn1/JPn2(n=1~8)は各チャンネルを RS485/422 で使用する場合のドライバスルーレートを設定するジャンパです。ジャンパ番号は(数字のみで)シルク表示されています。ジャンパ設定とスルーレートの関係は表 7-12をご参照ください。0 チップ抵抗を取り付けた場合 ON, 取り外した場合 OFF となります。出荷時には 500kbps にスルーレート制限されています。

表 7-12 JPn1/JPn2 設定とスルーレート

| JPn1 | JPn2 | スルーレート         |

|------|------|----------------|

| OFF  | OFF  | 115kbps        |

| OFF  | ON   | 10Mbps         |

| ON   | OFF  | 500kbps(出荷時設定) |

#### 《注意》

表に示されていない組み合わせ(JPn1/JPn2 両方を ON) の設定はしないようご注意ください。ジャンパを通して電源が短絡されるため、HT3080 のパターン焼損等の事故につながる可能性があります。

### 7.3.6 JPn3/JPn4

JPn3/JPn4(n=1~8)は、各チャンネルを RS232C で使用する場合のオートパワーダウン機能設定ジャンパです。ジャンパ番号は(数字のみで)シルク表示されています。ジャンパ設定とオートパワーダウン機能の関係は表 7-13をご参照ください。0 チップ抵抗を取り付けた場合 ON, 取り外した場合 OFF となります。出荷時にはオートパワーダウン機能は無効に設定されています。

オートパワーダウンが有効となっている場合、各チャンネルの RS232C レベル入力に 信号が観測されないと RS232C ドライバ出力がオフとなります。

表 7-13 JPn3/JPn4 設定とオートパワーダウン

| JPn3 | JPn4 | オートパワーダウン機能      |

|------|------|------------------|

| OFF  | ON   | オートパワーダウン有効      |

| ON   | OFF  | オートパワーダウン無効(出荷時) |

### 《注意》

JPn3/JPn4 両方を ON に設定しないようご注意ください。ジャンパを通して電源が短絡されるため、HT3080 のパターン焼損等の事故につながる可能性があります。また JPn3/JPn4 両方を OFF にすると RS232C ドライバの制御入力端子がオープンとなり動作が不安定となりますので、設定しないでください。

### 7.3.7 JPn5

JPn5(n=1~8)は、各チャンネルの受信信号を TTL レベルで使用する場合に、RS485 レシーバを通さず、直接 XR16L788 の Rxn 入力に接続するためのジャンパです。ジャンパ番号は(数字のみで)シルク表示されています。 0 チップ抵抗を取り付けた場合 ON, 取り外した場合 OFF となります。出荷時このジャンパは OFF に設定されています。 JPn5 を ON にする場合は、RS485 レシーバの出力と競合しないよう、JPn0 を TTL(Direct)の設定にしてください。(図 7-5参照)

### 7.3.8 JPn6

JPn6( $n=1\sim8$ )は、各チャンネルの送信信号を TTL レベルで使用する場合に、RS485ドライバ出力を使用せず、直接 XR16L788 の Txn 出力に接続するためのジャンパです。ジャンパ番号は(数字のみで)シルク表示されています。0 チップ抵抗を取り付けた場合 ON, 取り外した場合 OFF となります。出荷時このジャンパは OFF に設定されています。JPn6 を ON にする場合は、RS485ドライバの出力と競合しないよう、該当チャンネルの RTS をソフトウェアでアクティブにしないようご注意ください。

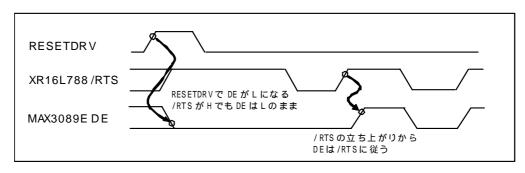

## 7.4 RS485 出力ドライバ制御

HT3080 では RS485 出力ドライバの ON/OFF を RTS で制御します。

自動 RS485 ハーフデュプレクス機能を有効にすると、XR16L788 は送信時に/RTS(または/DTR)を H にし、送信後 L に戻します。RS485 の出力ドライバ MAX3089E の送信ドライバイネーブル入力(DE)は、H のとき出力ドライバがアクティブとなるため、基本的には XR16L788 の/RTS 出力をドライバの DE 入力に接続すればよいのですが、ハードウェアリセット時に XR16L788 の/RTS は H となるためドライバ出力がアクティブになってしまいます。

このため HT3080 ではハードウェアリセット後 MAX3089E の DE 入力を L とし、該 当チャンネルの/RTS 信号が H L H と遷移してから DE 入力を/RTS で制御する回路を各チャンネルに付加しています。

図 7-6に RESETDRV、/RTS の変化に対する DE の状態変化を波形で示します。

図 7-6 RS485 出力イネーブル信号の制御

RS485 をフルデュプレクスで使用する場合も、出力ドライバをアクティブにするために/RTS を H L H と変化させる必要があります。/RTS の制御については8.2.8項をご参照ください。

## 7.5 RS485 ハーフ・フルデュプレクス切替

HT3080 では RS485 のハーフ・フルデュプレクス切替を各チャンネルの/DTR で制御します。各チャンネルの/DTR が MAX3089E の  $H/\overline{F}$  端子に接続されており、/DTR が アクティブの場合はフルデュプレクス、インアクティブの場合はハーフデュプレクス となります。/DTR の制御については8.2.8項をご参照ください。

## 7.6 タイマ外部クロック入力

XR16L788 のタイマクロック入力 TMRCK には、オンボードのボーレートクロック発振回路のほか外部クロックを接続することも可能です。外部クロックを使用する場合は R90 に 0 のチップ抵抗を取り付けると、PC/104 バスの SYSCLK を XR16L788の TMRCK に接続することができます。(出荷時 R90 には部品が実装されていません。基板裏面シルクで 90 と表示されています。)

## 8内蔵レジスタ

この章では、HT3080 に採用している XR16L788 のレジスタについて説明します。 HT3080 は I/O アドレス空間に XR16L788 のレジスタ 144 バイトを占有し、そのベースアドレスを JP1~4 で設定します。同時に使用する他の PC/104 モジュールの占有 I/O アドレスと重複しないようご注意ください。HT3080 はアドレスデコードを SA[15:0]までの 16 ビットで行っていますが、他の PC/104 モジュールは SA[10:0]までをデコードに使用している場合があります。

たとえば SA[10:0]までをデコードに使用しているボードの占有アドレスが 300H から 16 バイトの場合、そのイメージは B00H、1300H、1B00H…等にも存在しますので、HT3080 のベースアドレスは 300H だけでなく B00H に設定することもできません。

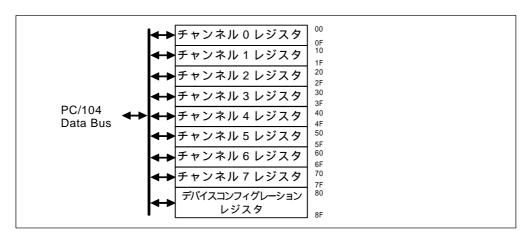

## 8.1 レジスタマップ

図 8-1に XR16L788 のレジスタの概要を示します。XR16L788 のレジスタは各チャンネルごとに用意されている UART チャンネルコンフィグレーションレジスタと、デバイス全体の設定を行うデバイスコンフィグレーションレジスタで構成されています。 各チャンネルの UART チャンネルコンフィグレーションレジスタのうち先頭 8 バイトは 16550 互換です。

図 8-1 XR16L788 のレジスタ概要

## 8.2 UART チャンネルコンフィグレーションレジスタ

表 8-1に各チャンネルの UART チャンネルコンフィグレーションレジスタのアドレスマップを示します。先頭の 8 つのレジスタは 16550 互換レジスタ、それ以降のレジスタが拡張されたレジスタとなっています。互換レジスタにもビット機能が拡張された箇所がありますので、16550 用に作成されたプログラムを HT3080 用に書き換えする場合は注意が必要です。

表 8-1 UART チャンネルコンフィグレーションレジスタアドレスマップ

| SA3 | SA2 | SA1 | SA0 | ReadWrite | レジスタ     | 機能                            |

|-----|-----|-----|-----|-----------|----------|-------------------------------|

| 0   | 0   | 0   | 0   | R/W       | DLL      | ディバイザラッチ LSB(LCR[7]=1 の場合)    |

| 0   | 0   | 0   | 1   | R/W       | DLM      | ディバイザラッチ MSB(LCR[7]=1 の場合)    |

| 0   | 0   | 0   | 0   | RO        | RHR      | 受信ホールディングレジスタ(LCR[7]=0 の場合)   |

| 0   | 0   | 0   | 0   | WO        | THR      | 送信ホールディングレジスタ(LCR[7]=0 の場合)   |

| 0   | 0   | 0   | 1   | R/W       | IER      | インタラプトイネーブルレジスタ(LCR[7]=0 の場合) |

| 0   | 0   | 1   | 0   | RO        | ISR      | インタラプトステータスレジスタ               |

| 0   | 0   | 1   | 0   | WO        | FCR      | FIFO コントロールレジスタ               |

| 0   | 0   | 1   | 1   | R/W       | LCR      | ラインコントロールレジスタ                 |

| 0   | 1   | 0   | 0   | R/W       | MCR      | モデムコントロールレジスタ                 |

| 0   | 1   | 0   | 1   | RO        | LSR      | ラインステータスレジスタ                  |

| 0   | 1   | 1   | 0   | RO        | MSR      | モデムステータスレジスタ                  |

| 0   | 1   | 1   | 0   | WO        | RS485DLY | RS485 ターンアラウンドディレイレジスタ        |

| 0   | 1   | 1   | 1   | R/W       | SPR      | スクラッチパッドレジスタ                  |

| 1   | 0   | 0   | 0   | R/W       | FCTR     | フィーチャーコントロールレジスタ              |

| 1   | 0   | 0   | 1   | R/W       | EFR      | エンハンスドファンクションレジスタ             |

| 1   | 0   | 1   | 0   | RO        | TXCNT    | 送信 FIFO レベルカウンタ               |

| 1   | 0   | 1   | 0   | WO        | TXTRG    | 送信 FIFO トリガレベル                |

| 1   | 0   | 1   | 1   | RO        | RXCNT    | 受信 FIFO レベルカウンタ               |

| 1   | 0   | 1   | 1   | WO        | RXTRG    | 受信 FIFO トリガレベル                |

| 1   | 1   | 0   | 0   | WO        | Xoff1    | Xoff キャラクタ 1                  |

| 1   | 1   | 0   | 0   | RO        | Xchar    | X 制御キャラクタレジスタ                 |

| 1   | 1   | 0   | 1   | WO        | Xoff2    | Xoff キャラクタ 2                  |

| 1   | 1   | 1   | 0   | WO        | Xon1     | Xon キャラクタ 1                   |

| 1   | 1   | 1   | 1   | WO        | xon2     | Xon キャラクタ 2                   |

各レジスタ詳細については、XR16L788のデータシートをご参照ください。

### 8.2.1 RHR

RHR は受信データを読み出しする 8bit のレジスタで、読み出し専用です。同じアドレスへの書き込みは THR への書き込みとなります。RHR と DLL レジスタは同じアドレスにマッピングされているため、RHR をアクセスする場合は LCR の bit7 に 0 を設定する必要があります。

### 8.2.2 THR

THR は送信データを書き込みする 8bit のレジスタで、書き込み専用です。同じアドレスからのデータ読み出しでは、RHR の値を読み出します。THR と DLL レジスタは同じアドレスにマッピングされているため、THR をアクセスする場合は、LCR の bit7 に 0 を設定する必要があります。

THR への書き込みは、THR 割り込み時または LSR の THREmpty が 1 のときに行ってください。

### 8.2.3 DLL, DLM

DLL/DLM レジスタはボーレートジェネレータの分周比を設定するレジスタで DLL が LSB、DLM が MSB となる 16bit レジスタを構成しています。

ボーレートは 14.7456MHz を DLL/DLM レジスタ設定値で分周して作成されますが、 プリスケーラの設定(MCR レジスタの BRG Prescaler ビット)とサンプリングクロック の設定(8XMODE レジスタの UARTn ビット)にも影響をうけます。分周比の計算式と これらの設定値との関係を表 8-2に示します。

| BRG Prescaler | 8XMODE | 分周比                    |

|---------------|--------|------------------------|

| 0             | 0      | 14745600/(ボーレート設定値×16) |

| 0             | 1      | 14745600/(ボーレート設定値×8)  |

| 1             | 0      | 3686400/(ボーレート設定値×16)  |

| 1             | 1      | 3686400/(ボーレート設定値×8)   |

表 8-2 分周比計算式

DLL/DLM レジスタは THR/RHR/IER と同じアドレスにマッピングされているため、 DLL/DLM レジスタをアクセスする場合は、LCR の bit7 に 1 を設定する必要があります。 なおリセット時 DLL/DLM の値は不定です。

### 《注意》

MCR レジスタの BRGPrescaler ビットは 16550 互換レジスタに割り当てされていますが XR16L788 の拡張機能です。ソフトウェア移植の際にはご注意ください。また UART 用のシステムクロックや分周比設定値の計算は PC/AT とは異なります。PC/AT の場合、分周比は  $1843200/(ボーレート設定値 \times 16)$ で計算されます。

### 8.2.4 IER

IER は割り込み禁止・許可を設定する 8bit のレジスタです。IER と DLM レジスタは同じアドレスにマッピングされているため、IER をアクセスする場合は、LCR の bit7 に 0 を設定する必要があります。

IERのビット構成を図 8-2に、各ビットの機能を表 8-3に示します。

| bit7               | bit6               | bit5                | bit4 | bit3                              | bit2                                | bit1               | bit0               |

|--------------------|--------------------|---------------------|------|-----------------------------------|-------------------------------------|--------------------|--------------------|

| CTS Int.<br>Enable | RTS Int.<br>Enable | Xoff Int.<br>Enable | 0    | Modem<br>Status<br>Int.<br>Enable | RX Line<br>Status<br>Int.<br>Enable | THR Int.<br>Enable | RHR Int.<br>Enable |

図 8-2 IER の構成

表 8-3 IER の各ビット機能

| bit              | 説明                                           |

|------------------|----------------------------------------------|

| RHR Int. Enable  | nonFIFO モードでは RHR に受信データがある場合、FIFO モードでは受信   |

|                  | FIFO が設定されたトリガレベルに達した場合に割り込みを発生します。          |

| THR Int. Enable  | THRが空となった場合または送信FIFOが設定されたトリガレベルを下回っ         |

|                  | た場合に割り込みを発生します。                              |

| RX Line Status   | LSR のビット 1~4 のいずれかが 1 になった場合に割り込みを発生します。     |

| Int. Enable      |                                              |

| Modem Status     | MSR のビット $0~3$ のいずれかが $1$ になった場合に割り込みを発生します。 |

| Int. Enable      |                                              |

| Xoff Int. Enable | Xoff/Xon/特別キャラクタ受信で割り込みを発生します。この機能を使用する      |

|                  | 場合は EFR の bit4 に 1 を設定する必要があります。             |

| RTS Int. Enable  | オートハードフロー制御を使用する設定で、/RTS または/DTR がアクティブ      |

|                  | からインアクティブになった場合に割り込みを発生します。この機能を使用           |

|                  | する場合は EFR の bit4 に 1 を設定する必要があります。           |

| CTS Int. Enable  | オートハードフロー制御を使用する設定で、/CTS または/DSR がアクティブ      |

|                  | からインアクティブになった場合に割り込みを発生します。この機能を使用           |

|                  | する場合は EFR の bit4 に 1 を設定する必要があります。           |

0 が設定されたビットの割り込みは禁止、1 が設定されたビットの割り込みは許可されます。 リセット後 IER は 00H に初期化されます。

### 8.2.5 ISR

ISR は割り込みのステータスを示す 8bit のレジスタで、読み出し専用です。同じアドレスへの書き込みは FCR への書き込みとなります。 ISR のビット構成を図 8-3に示します。

| bit7   | bit6   | bit5   | bit4   | bit3   | bit2   | bit1   | bit0   |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FIFOs  | FIFOs  | INT    | INT    | INT    | INT    | INT    | INT    |

| Enable | Enable | Source | Source | Source | Source | Source | Source |

| Enable | Enable | Bit-5  | Bit-4  | Bit-3  | Bit-2  | Bit-1  | Bit-0  |

図 8-3 ISR の構成

FIFOsEnable ビットには FIFO が有効な場合は 1、無効の場合は 0 が読み出されます。 INT Source フィールドは 6 ビットで構成され、ISR の読み出しでその時点で一番高い 優先順位の割り込み要因を返します。その他の割り込みはその割り込みが処理されるまで保留となります。

表 8-4 割り込み要因とプライオリティレベル

| プライオリティ | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 割り込み要因                                               |

|---------|------|------|------|------|------|------|------------------------------------------------------|

| 1       | 0    | 0    | 0    | 1    | 1    | 0    | LSRbit1,2,3,4 に変化があった場合                              |

| 2       | 0    | 0    | 0    | 1    | 0    | 0    | 受信トリガレベルによる RxDataRDY                                |

| 3       | 0    | 0    | 1    | 1    | 0    | 0    | タイムアウトによる RxRDY                                      |

| 4       | 0    | 0    | 0    | 0    | 1    | 0    | THRが空になった場合(オートRS485 機能を有効にして<br>いる場合は TSR が空になった場合) |

| 5       | 0    | 0    | 0    | 0    | 0    | 0    | MSR の bit0,1,2,3 に変化があった場合                           |

| 6       | 0    | 1    | 0    | 0    | 0    | 0    | Xon/Xoff/特別キャラクタが検出された場合                             |

| 7       | 1    | 0    | 0    | 0    | 0    | 0    | オートハードフロー制御ラインがアクティブからインア<br>クティブになった場合              |

| -       | 0    | 0    | 0    | 0    | 0    | 1    | なし                                                   |

表 8-4に INT Source フィールドの値と、割り込み要因を示します。複数の割り込み条件が成立した場合は、表中の優先順位が高いものから通知されます。ISR の bit4、bit5 は拡張機能のため、この機能を使用する場合は EFR の bit4 に 1 を設定する必要があります。各割り込みの発生条件、クリア条件を表 8-5に示します。

表 8-5 割り込みの発生、クリア条件

| 割り込み             | 発生                | クリア                  |

|------------------|-------------------|----------------------|

| LSR              | LSRbit1/2/3/4 の変化 | LSR 読み出したとき          |

| RxRDY            | 受信トリガレベル          | 受信 FIFO がトリガレベルを下回   |

|                  |                   | ったとき                 |

| RxRDY            | 受信タイムアウト          | RHR の読み出し            |

| TxRDY            | THR が空となったとき(オート  | ISR 読み出しまたは THR への書き |

|                  | RS485 機能が有効な場合は   | 込み                   |

|                  | TSR が空となったとき)     |                      |

| MSR              | MSRbit0/1/2/3 の変化 | MSR の読み出し            |

| Xon/Xoff         | Xon/Xoff 受信       | ISR 読み出し             |

| SpecialCharacter | 特別キャラクタ受信         | ISR 読み出しまたは次のキャラク    |

|                  |                   | タ受信                  |

| オートハードフロー        | 制御入出力の変化          | MSR の読み出し            |

### 8.2.6 FCR

FCR は FIFO の動作を設定する 8bit のレジスタで、書き込み専用です。同じアドレスの読み出しは ISR の読み出しとなります。 FCR のビット構成を図 8-4に示します。

| bit7    | bit6    | bit5    | bit4    | bit3 | bit2    | bit1    | bit0   |

|---------|---------|---------|---------|------|---------|---------|--------|

| RX FIFO | RX FIFO | TX FIFO | TX FIFO |      | TX FIFO | RX FIFO | FIFOs  |

| Trigger | Trigger | Trigger | Trigger | -    | Reset   | Reset   | Enable |

図 8-4 FCR の構成

FCR の各ビット機能を表 8-6に示します。FIFO のトリガレベル設定は FCTR の bit6,7 の設定により異なります。表 8-7をご参照ください。 FCR の bit4、bit5 は拡張機能のため、この機能を使用する場合は EFR の bit4 に 1 を設定する必要があります。 リセット時に FCR は 00H に初期化されます。

表 8-6 FCR の各ビット機能

| bit             | 説明                                                                                    |

|-----------------|---------------------------------------------------------------------------------------|

| FIFOs Enable    | 0:送受信 FIFO を禁止します。 (初期値)<br>1:送受信 FIFO を許可します。<br>このビットが 0 の場合は FCR のその他のビットは設定できません。 |

| RX FIFO Reset   | 1 を書き込むと受信 FIFO をリセットします。リセット後このビットは 0 に戻ります。                                         |

| TX FIFO Reset   | 1 を書き込むと送信 FIFO をリセットします。リセット後このビットは 0 に戻ります。                                         |

| TX FIFO Trigger |                                                                                       |

| Select          | の bit6,7 の設定によって異なります。                                                                |

| RX FIFO Trigger | 受信 FIFO のトリガレベルを選択します。選択されるトリガレベルは FCTR                                               |

| Select          | の bit6,7 の設定によって異なります。                                                                |

表 8-7 FIFO トリガテーブルとトリガレベル設定値

| トリガテーブル | FC   | TR   |      | FCR  |      | トリガ  | レベル       |           |

|---------|------|------|------|------|------|------|-----------|-----------|

| トリカテーノル | Bit7 | Bit6 | Bit7 | Bit6 | Bit5 | Bit4 | 受信        | 送信        |

|         |      |      |      |      | 0    | 0    |           | 1         |

|         |      |      | 0    | 0    |      |      | 1         |           |

| Table A | 0    | 0    | 0    | 1    |      |      | 4         |           |

|         |      |      | 1    | 0    |      |      | 8         |           |

|         |      |      | 1    | 1    |      |      | 14        |           |

|         |      |      |      |      | 0    | 0    |           | 16        |

|         |      |      |      |      | 0    | 1    |           | 8         |

|         |      |      |      |      | 1    | 0    |           | 24        |

| Table B | 0    | 1    |      |      | 1    | 1    |           | 30        |

| таше в  |      |      | 0    | 0    |      |      | 8         |           |

|         |      |      | 0    | 1    |      |      | 16        |           |

|         |      |      | 1    | 0    |      |      | 24        |           |

|         |      |      | 1    | 1    |      |      | 28        |           |

|         |      |      |      |      | 0    | 0    |           | 8         |

|         |      |      |      |      | 0    | 1    |           | 16        |

|         |      |      |      |      | 1    | 0    |           | 32        |

| Table C | 1    | 0    |      |      | 1    | 1    |           | 56        |

| rable C | 1    | U    | 0    | 0    |      |      | 8         |           |

|         |      |      | 0    | 1    |      |      | 16        |           |

|         |      |      | 1    | 0    |      |      | 56        |           |

|         |      |      | 1    | 1    |      |      | 60        |           |

| Table D | 1    | 1    | X    | X    | X    | X    | RXTRG で設定 | TXTRG で設定 |

### 8.2.7 LCR

LCR は非同期通信フォーマットを設定する 8bit のレジスタです。FCR のビット構成を図 8-5に、各ビットの機能を表 8-8に示します。リセット時 LCR は 00H に初期化されます。

| bit7              | bit6            | bit5       | bit4           | bit3             | bit2      | bit1                    | bit0                    |  |

|-------------------|-----------------|------------|----------------|------------------|-----------|-------------------------|-------------------------|--|

| Divisor<br>Enable | Set TX<br>Break | Set Parity | Even<br>Parity | Parity<br>Enable | Stop Bits | Word<br>Length<br>bit 1 | Word<br>Length<br>bit 0 |  |

図 8-5 LCR の構成

表 8-8 LCR の各ビット機能

| bit              | 説明                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Word Length[1:0] | 通信のキャラクタ長を設定します。<br>00:5bit<br>01:6bit<br>10:7bit<br>11:8bit                                                                    |

| Stop Bits        | ストップビット長を設定します。<br>0:1stop bit<br>1:2stop bit(キャラクタ長が 5bit の場合は 1.5stop bit)                                                    |

| Parity Enable    | 0:パリティを使用しません。<br>1:送信時パリティを付加し、受信時はパリティエラーチェックを行います。                                                                           |

| Even Parity      | 0:奇数パリティ (ODD)<br>1:偶数パリティ (EVEN)                                                                                               |

| Set Parity       | Parity Enable ビットが 1 の場合に、<br>0:パリティの計算を行います。<br>1:強制的にパリティの値を設定します。奇数パリティ設定の場合はパリティ<br>ビットを 1 に、偶数パリティ設定の場合はパリティビットを 0 に設定します。 |

| SetTX Break      | 1 を設定するとこのビットを 0 に戻すまで送信出力をブレーク状態にします。                                                                                          |

| Divisor Enable   | 0:RHR/THR をアクセスすることができます。<br>1:DLL/DLM をアクセスすることができます。                                                                          |

#### 8.2.8 MCR

MCR はモデムインターフェース信号を制御する 8bit のレジスタです。MCR のビット構成を図 8-6に、各ビットの機能を表 8-9に示します。 リセット時 MCR は 00H に初期化されます。

| bit7      | bit6       | bit5    | bit4     | bit3 | bit2     | bit1    | bit0    |

|-----------|------------|---------|----------|------|----------|---------|---------|

| BRG       | IR Enable  | Xon Any | Internal |      | Flow Sel | RTS     | DTR     |

| Prescaler | ik Ellable | Aon Any | Loopback | -    | Flow Sei | Control | Control |

図 8-6 MCR の構成

#### 表 8-9 MCR の各ビット機能

| bit           | 説明                                           |

|---------------|----------------------------------------------|

| BRG Prescaler | 0:プリスケーラ分周比を 1 に設定します。                       |

| BRG Prescaler | 1:プリスケーラ分周比を 4 に設定します。                       |

| IR Enable     | 0:通常のモデム送受信インターフェースを選択します。                   |

| TR Enable     | 1:IrDA モードとなりますが、HT3080 ではサポートしていません。        |

| Xon Any       | このビットを 1 に設定すると、受信キャラクタが Xon 以外でもデータ送信       |

| Aon Any       | を再開します。                                      |

| Internal      | 0:ループバック状態を解除します。                            |

| Loopback      | 1:ローカルループバック状態にします。                          |

|               | ハードフロー制御に使う信号を選択します。                         |

| Flow Sel      | 0:RTS/CTS を使用します。                            |

|               | 1:DTR/DSR を使用します。                            |

|               | RTS 端子のレベルを制御します。 RS485 モード時の機能は7.4をご参照ください。 |

| RTS control   | 0:RTS をインアクティブにします。                          |

|               | 1:RTS をアクティブにします。                            |

|               | DTR 端子のレベルを制御します。RS485 モード時の機能は7.5をご参照ください。  |

| DTR control   | 0:DTR をインアクティブにします。                          |

|               | 1:DTR をアクティブにします。                            |

MCR の bit2、bit5、bit6、bit7 は拡張機能のため、この機能を使用する場合は EFR の bit4 に 1 を設定する必要があります。

#### 8.2.9 LSR

LSR は UART とホスト間のデータ転送ステータスを提供する 8bit のレジスタです。 LSR のビット構成を図 8-6に、各ビットの機能を表 8-9に示します。リセット時 MCR は 60H に初期化されます。

| bit7             | bit6         | bit5         | bit4     | bit3                   | bit2               | bit1          | bit0            |

|------------------|--------------|--------------|----------|------------------------|--------------------|---------------|-----------------|

| RX FIFO<br>ERROR | TSR<br>Empty | THR<br>Empty | RX Break | RX<br>Framing<br>Error | RX Parity<br>Error | Rx<br>OverRun | RxData<br>Ready |

図 8-7 LSR の構成

表 8-10 LSR の各ビット機能

| bit                 | 説明                                                                                           |

|---------------------|----------------------------------------------------------------------------------------------|

| RX FIFO Error       | 0:受信 FIFO にエラーがないことを示します。<br>1:受信 FIFO になんらかのエラーがあることを示します。FIFO からエラーがなくなるとこのビットはクリアされます。    |

| TSR Empty           | 0:THR または TSR にデータがある場合<br>1:送信アイドル状態を示します。                                                  |

| THR Empty           | 0:THR にデータがある場合<br>1:THR または TXFIFO に空きがある場合                                                 |

| RX Break            | 0:ブレーク状態ではないことを示します。<br>1:ブレーク信号を受信したことを示します。FIFO モードでは FIFO には 1<br>バイトのみプレークキャラクタがロードされます。 |

| RX Framing<br>Error | 0:フレーミングエラーなし<br>1:フレーミングエラー                                                                 |

| RX Parity Error     | 0:パリティエラーなし<br>1:パリティエラー検出                                                                   |

| RX Overrun<br>Error | 0:オーバーランエラーなし<br>1:オーバーランエラー検出                                                               |

| RX Data Ready       | 0:受信データなし<br>1:受信データあり                                                                       |

#### 8.2.10 MSR

MSR はモデムインターフェース信号の状態を示す 8bit のレジスタで、読み出し専用です。同じアドレスへの書き込みは RS485DLY レジスタへの書き込みとなります。 MSR のビット構成を図 8-8に、各ビットの機能を表 8-11に示します。

| bit7 | bit6 | bit5 | bit4 | bit3   | bit2   | bit1   | bit0   |

|------|------|------|------|--------|--------|--------|--------|

| CD   | RI   | DSR  | СТС  | CD     | RI     | DSR    | CTS    |

| CD   | KI   | DSK  | CIS  | Change | Change | Change | Change |

図 8-8 MSR の構成

表 8-11 MSR の各ビット機能

| bit        | 説明                                                               |

|------------|------------------------------------------------------------------|

| CD         | 0:CD がインアクティブ                                                    |

| RI         | 1:CD がアクティブ<br>0:RI がインアクティブ                                     |

|            | 1:RI がアクティブ                                                      |

| DSR        | 0:DSR がインアクティブ<br>1DSR がアクティブ                                    |

| CTS        | 0:CTS がインアクティブ                                                   |

|            | 1:CTS がアクティブ                                                     |

| CD Change  | 0:CD の状態に変化がないことを示します。<br> 1:CD の状態に変化があったことを示します。このレジスタの読み出しで 0 |

| CD Change  | にリセットされます。                                                       |

|            | 0:RI の状態に変化がないことを示します。                                           |

| RI Change  | 1:RI の状態に変化があったことを示します。このレジスタの読み出しで 0                            |

|            | にリセットされます。                                                       |

| DCD CI     | 0:DSR の状態に変化がないことを示します。                                          |

| DSR Change | 1:DSR の状態に変化があったことを示します。このレジスタの読み出しで 0  <br> にリセットされます。          |

|            | O:CTS の状態に変化がないことを示します。                                          |

| CTS Change | 1:CTS の状態に変化があったことを示します。このレジスタの読み出しで 0                           |

|            | にリセットされます。                                                       |

#### 8.2.11 RS485DLY

RS485DLY レジスタは、オート RS485 モードの場合に送信から受信への切替時間を 設定する書き込み専用レジスタです。同じアドレスの読み出しは MSR レジスタから の読み出しとなります。図 8-9に RS485DLY レジスタのビット構成を示します。

| b | it7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|---|-----|------|------|------|------|------|------|------|

| D | LY3 | DLY2 | DLY1 | DLY0 | 0    | 0    | 0    | 0    |

図 8-9 RS485DLY の構成

DLY[3:0]の 4 ビットで 0 から 15 までの値を設定可能です。最終データのストップビット送信後から DLY で指定された値  $\times$  1 ビット時間のディレイ後に RTS を切り替えて RS485 出力をハイインピーダンスにします。

### 8.2.12 SPR

SPR はユーザが自由に使用することができる 8bit のスクラッチパッドレジスタです。 リセット時は FFH に初期化されます。

#### 8.2.13 FCTR

FCTR は拡張された機能の設定を行う 8bit のレジスタです。図 8-10に FCTR のビット構成を、表 8-12に各ビット機能を示します。リセット時 FCTR は 00H に初期化されます。

| bit7              | bit6              | bit5                    | bit4                  | bit3              | bit2              | bit1              | bit0              |  |

|-------------------|-------------------|-------------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|--|

| TRG<br>Table<br>1 | TRG<br>Table<br>0 | AUTO<br>RS485<br>Enable | Invert IR<br>RX Input | RTS/DTR<br>Hyst 3 | RTS/DTR<br>Hyst 2 | RTS/DTR<br>Hyst 1 | RTS/DTR<br>Hyst 0 |  |

図 8-10 FCTR の構成

表 8-12 FCTR の各ビット機能

| bit            | 説明                                     |

|----------------|----------------------------------------|

| TDC Table[1:0] | FIFO のトリガテーブルを選択します。FIFO のトリガレベルについては  |

| TRG Table[1:0] | 表 8-7をご参照ください。                         |

| AUTO RS485     | 0:AUTO RS485 ハーフデュプレクス制御を無効にします。       |

| Enable         | 1:AUTO RS485 ハーフデュプレクス制御を有効にします。       |

| Invert IR      | 0:受信入力をアクティブハイの IrDA 入力とします。           |

| RX input       | 1:受信入力をアクティブローの IrDA 入力とします。           |

| DEC/DED        | ハードフロー制御のトリガテーブル D が選択されている場合に、受信 FIFO |

| RTS/DTR        | のトリガレベルに対する RTS/DTR のヒステリシスを設定します。     |

| Hyst[3:0]      | ヒステリシスの設定については表 8-13をご参照ください。          |

表 8-13 ヒステリシスレベルの設定

| Hyst3 | Hyst2 | Hyst1 | Hyst0 | RTS/DTR ヒステリシス<br>(キャラクタ) |  |  |  |

|-------|-------|-------|-------|---------------------------|--|--|--|

| 0     | 0     | 0     | 0     | 0                         |  |  |  |

| 0     | 0     | 0     | 1     | 4                         |  |  |  |

| 0     | 0     | 1     | 0     | 6                         |  |  |  |

| 0     | 0     | 1     | 1     | 8                         |  |  |  |

| 0     | 1     | 0     | 0     | 8                         |  |  |  |

| 0     | 1     | 0     | 1     | 16                        |  |  |  |

| 0     | 1     | 1     | 0     | 24                        |  |  |  |

| 0     | 1     | 1     | 1     | 32                        |  |  |  |

| 1     | 1     | 0     | 0     | 12                        |  |  |  |

| 1     | 1     | 0     | 1     | 20                        |  |  |  |

| 1     | 1     | 1     | 0     | 28                        |  |  |  |

| 1     | 1     | 1     | 1     | 36                        |  |  |  |

| 1     | 0     | 0     | 0     | 40                        |  |  |  |

| 1     | 0     | 0     | 1     | 44                        |  |  |  |

| 1     | 0     | 1     | 0     | 48                        |  |  |  |

| 1     | 0     | 1     | 1     | 52                        |  |  |  |

### 8.2.14 EFR

EFR は拡張された機能の設定を行う 8bit のレジスタです。図 8-11に EFR のビット構成を、表 8-14に各ビット機能を示します。 リセット時 EFR は 00H に初期化されます。

|   | bit7    | bit6    | bit5    | bit4     | bit3      | bit2      | bit1      | bit0      |

|---|---------|---------|---------|----------|-----------|-----------|-----------|-----------|

| ĺ | Auto    | Auto    | Special | Enhanced | Software  | Software  | Software  | Softwre   |

|   | CTS/DSR | RTS/DTR | Char    | Function | Flow Cntl | Flow Cntl | Flow Cntl | Flow Cntl |

|   | Enable  | Enable  | Select  | Enable   | 3         | 2         | 1         | 0         |

図 8-11 EFR の構成

#### 表 8-14 EFR の各ビット機能

| bit                         | 説明                                                                                                                  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------|

| AutoCTS/DSR<br>Enable       | CTS または DSR による送信ハードウェアフロー制御を使用するかどうかを<br>設定します。<br>0:使用しない<br>1:使用する<br>CTS/DSR のどちらを使用するかは MCR の bit2 で設定します。     |

| Auto RTS/DTR<br>Enable      | RTS または DTR による受信ハードウェアフロー制御を使用するかどうかを<br>設定します。<br>0:使用しない<br>1:使用する<br>RTS/DTR のどちらを使用するかは MCR の bit2 で設定します。     |

| Special Char<br>Select      | 0:特別キャラクタ検出を行いません。<br>1:特別キャラクタ検出を行います。                                                                             |

| Enhanced<br>Function Enable | このビットを 1 にすると、IER の bit4-7、ISR の bit4,5、FCR の bit4,5、MCR の bit5-7 を変更することができます。このビットを 0 にすると変更された値は保持され、変更できなくなります。 |

| Software<br>Flow Cntl[3:0]  | 4 ビットの組み合わせでソフトウェアフロー制御の機能を設定します。詳細は表 8-15をご参照ください。                                                                 |

#### 表 8-15 ソフトウェアフロー制御の設定

| Software Flow Cntl |      |      |      | 平信フロー制御                    | 送信フロー制御                                                     |  |  |  |  |  |  |

|--------------------|------|------|------|----------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| bit3               | bit2 | bit1 | bit0 | 受信フロー制御                    | た旧ノロ 咿咿                                                     |  |  |  |  |  |  |

| 0                  | 0    | 0    | 0    | フロー制御なし                    | フロー制御なし                                                     |  |  |  |  |  |  |

| 0                  | 0    | 0    | 1    | フロー制御なし                    | Xon2/Xoff2 を検出                                              |  |  |  |  |  |  |

| 0                  | 0    | 1    | 0    | フロー制御なし                    | Xon1/Xoff1 を検出                                              |  |  |  |  |  |  |

| 1                  | 0    | 0    | 0    | Xon1/Xoff1 を送信             | フロー制御なし                                                     |  |  |  |  |  |  |

| 1                  | 0    | 0    | 1    | Xon1/Xoff1 を送信             | Xon2/Xoff2 を検出                                              |  |  |  |  |  |  |

| 1                  | 0    | 1    | 0    | Xon1/Xoff1 を送信             | Xon1/Xoff1 を検出                                              |  |  |  |  |  |  |

| 0                  | 1    | 0    | 0    | Xon2/Xoff2 を送信             | フロー制御なし                                                     |  |  |  |  |  |  |

| 0                  | 1    | 0    | 1    | Xon2/Xoff2 を送信             | Xon2/Xoff2 を検出                                              |  |  |  |  |  |  |

| 0                  | 1    | 1    | 0    | Xon2/Xoff2 を送信             | Xon1/Xoff1 を検出                                              |  |  |  |  |  |  |

| 1                  | 1    | 0    | 0    | Xon1と Xon2/Xoff1と Xoff2を送信 | フロー制御なし                                                     |  |  |  |  |  |  |

| 1                  | 1    | 0    | 1    | Xon1と Xon2/Xoff1と Xoff2を送信 | Xon2/Xoff2 を検出                                              |  |  |  |  |  |  |

| 1                  | 1    | 1    | 0    | Xon1と Xon2/Xoff1と Xoff2を送信 | Xon2/Xoff2 を検出                                              |  |  |  |  |  |  |

| 1                  | 0    | 1    | 1    | Xon1/Xoff1 を送信             | Xon1 または Xon2, Xoff1 または<br>Xoff2 を検出                       |  |  |  |  |  |  |

| 0                  | 1    | 1    | 1    | Xon2/Xoff2 を送信             | Xon1 または Xon2, Xoff1 または<br>Xoff2 を検出                       |  |  |  |  |  |  |

| 1                  | 1    | 1    | 1    | Xon1とXon2/Xoff1とXoff2を送信、  | Xon1 と Xon2 の連続 2 キャラクタ<br>または Xoff1 と Xoff2 の連続 2 キャラクタを検出 |  |  |  |  |  |  |

| 0                  | 0    | 1    | 1    | フロー制御なし、                   | Xon1 と Xon2 の連続 2 キャラクタ<br>または Xoff1 と Xoff2 の連続 2 キャラクタを検出 |  |  |  |  |  |  |

#### 8.2.15 TXCNT

TXCNT レジスタは送信 FIFO 内のキャラクタ数を示す 8bit の読み出し専用レジスタです。読み出しされる値は  $0 \sim 40 \text{H}$  です。

#### 8.2.16 TXTRG

TXTRG レジスタは送信 FIFO のトリガレベルを設定する 8bit の書き込み専用レジスタです。書き込み可能な設定値は  $0\sim40\mathrm{H}$  です。リセット時 TXTRG は  $00\mathrm{H}$  に初期化されます。

#### 8.2.17 RXCNT

RXCNT レジスタは受信 FIFO 内のキャラクタ数を示す 8bit の読み出し専用レジスタです。読み出しされる値は  $0 \sim 40 \text{H}$  です。

#### 8.2.18 RXTRG

RXTRG レジスタは受信 FIFO のトリガレベルを設定する 8bit の書き込み専用レジスタです。書き込み可能な設定値は  $0\sim40\mathrm{H}$  です。リセット時 RXTRG は  $00\mathrm{H}$  に初期化されます。

#### 8.2.19 XCHAR

XCHAR レジスタは Xon/Xoff 制御キャラクタ検出状態を示す 8bit の読み出し専用レジスタです。 XCHAR レジスタのビット構成を図 8-12に示します。

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1                  | bit0                   |

|------|------|------|------|------|------|-----------------------|------------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | Xon Det.<br>Indicator | Xoff Det.<br>Indicator |

図 8-12 XCHAR の構成

Xon Det. Indicator ビットは XON キャラクタの検出を、Xoff Det. Indicator ビットは XOFF キャラクタの検出時に 1 となります。これらのビットは XCHAR レジスタのリードで 0 にクリアされます。

#### 8.2.20 XOFF1

XOFF1 レジスタはソフトウェアフロー制御で使用する XOFF キャラクタを設定する 8bit のレジスタで、書き込み専用です。同じアドレスからのデータ読み出しでは、 XCHAR レジスタを読み出します。EFR[0:3]で設定される X 制御のモードについては 表 8-15をご参照ください。リセット時 XOFF1 は 00H に初期化されます。

#### 8.2.21 XOFF2

XOFF2 レジスタはソフトウェアフロー制御で使用する XOFF キャラクタを設定する 8bit のレジスタで、書き込み専用です。EFR[0:3]で設定される X 制御のモードについ ては表 8-15をご参照ください。リセット時 XOFF2 は 00H に初期化されます。

#### 8.2.22 XON1

XON1 レジスタはソフトウェアフロー制御で使用する XON キャラクタを設定する 8bit のレジスタで、書き込み専用です。EFR[0:3]で設定される X 制御のモードについ ては表 8-15をご参照ください。リセット時 XON1 は 00H に初期化されます。

#### 8.2.23 XON2

XON2 レジスタはソフトウェアフロー制御で使用する XON キャラクタを設定する 8bit のレジスタで、書き込み専用です。EFR[0:3]で設定される X 制御のモードについ ては表 8-15をご参照ください。リセット時 XON2 は 00H に初期化されます。

## 8.3 デバイスコンフィグレーションレジスタ